You are here: GSI Wiki>Epics Web>EpicsProjectsAndActivities>HardwarePlatforms>HadCon2>HadCon2MultipurposeControlsApi>HadCon2MultipurposeControlsProtocol>HadCon2MultipurposeControlsProtocolCmndApfel>HadConMultipurposeControlsProtocolCmndApfelDetailsOfTheProtocol (2015-05-27, PeterZumbruch)

Apfel - Details Of The Communication Protocol

Introduction

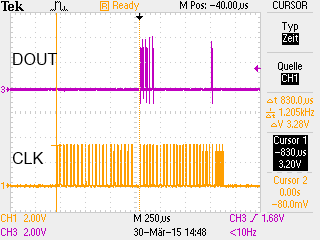

The communication with the APFEL chip on the signal levelMain

- DOUT low + CLK low

- DOUT high + CLK low

- DOUT high + CLK high

- DOUT low + CLK high

- DOUT low + CLK low

- DOUT low + CLK low

- DOUT high + CLK low

- DOUT high + CLK high

- DOUT low + CLK high

- DOUT low + CLK low

- ~25μs per bit

- → max 40kBit/s

- or 5μs per state change

- + 10μs

- → max 28kBit/s

- using artificial markers before and after the parser give

- a minimum of ~37μs per call

- typical values of ~1.2ms (w/o any output)

- typical values of ~12 ms (with output)

- typical values of ~15 ms (with error output)

- maximum 125ms (autocalibration)

- BIG - endian

- stream header

- the actual command sequence

- command specific sequences

- clear data input sequence, i.e.

- for each command sequence bit (22)

- write 1 clock sequence:

- equivalent to: write 1 low bit

- each 8 bit with 2 additional sequences of

- DOUT low + CLK low

- write 1 clock sequence:

- followed by 10 sequences of the same

- DOUT low + CLK low

- ⇒ summed up roughly ~620μs

- ⇒ measured ~620μs ~760-840μs

- for each command sequence bit (22)

- the set

- DOUT low + CLK low

- to allow side selection bit to change before any action

- DOUT low + CLK low

- the sequence

- DOUT low + CLK low

- DOUT high + CLK low

- DOUT high + CLK high

- DOUT high + CLK low ⇐ this is the only difference to a low bit sequence

- DOUT low + CLK low

- 4 command bits

- 10 value bits

- 8 chip id bits

- 3 clock cycles

- equivalent to 3 low bit sequences

- (optional) the complete readDac sequence

- read bit sequence for

- 2 leading bits

-

this have to be

this have to be 10(binary), to be correct

-

- 10 value bits

- 3 trailing bits

-

this have to be

this have to be 111(binary), to be correct

-

- so in total a bit stream of the form of

10 xx xxxx xxxx 111has to be read

- 2 leading bits

- followed by 3 clock cycles

- equiv. to 3 low bit

- DOUT low + CLK low

- Initial bit and the rest

- Initial bit

- since the APFEL needs first the falling clock endge to activate the output pad, the initial bit is read differently

- CLK high

- CLK low

- read PIN

- Remaining bit

- CLK high

- read PIN

- CLK low

- Initial bit

- 4 × 1024 = 4096 clock cycles

- 3 clock cycles

- 3 clock cycles

- command

set amplification -

Bits

Bits are represented by a sequence of 5 states of the pins DOUT and CLKHigh

Low

Measurements

execution times of the api

Endianness

commands

-

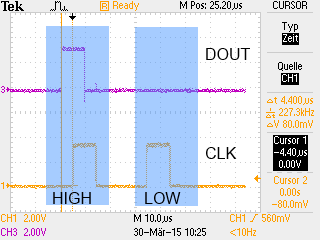

The full command sequence consists of:

stream header

-

The actual command sequence is prefixed by a stream header consisting of

command sequence

-

The bare command set of the APFEL protocol is a big-endian sequence of 22 bits:

command specific sequences

setDac

readDac

read bit sequence

auto calibration

test pulse - sequence

set/reset amplification

Example

-- PeterZumbruch - 31 Mar 2015

-- PeterZumbruch - 2015-05-27

| I | Attachment |

Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

Bits.png | manage | 5 K | 2015-03-31 - 09:43 | PeterZumbruch | Bit timing |

| |

CommandSequence.png | manage | 5 K | 2015-03-30 - 16:08 | PeterZumbruch | Apfel command sequence for Command E |

Please login to edit this topic

Topic revision: r5 - 2015-05-27, PeterZumbruch

- User Reference

- BeginnersStartHere

- EditingShorthand

- Macros

- MacrosQuickReference

- FormattedSearch

- QuerySearch

- DocumentGraphics

- SkinBrowser

- InstalledPlugins

- Admin Maintenance

- Reference Manual

- AdminToolsCategory

- InterWikis

- ManagingWebs

- SiteTools

- DefaultPreferences

- WebPreferences

- Categories

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)