You are here: GSI Wiki>Epics Web>EpicsProjectsAndActivities>HardwarePlatforms>HadCon (2018-03-15, PeterZumbruch)

HadCon a.k.a. HadControl a.k.a. HadShoPoMo

Introduction

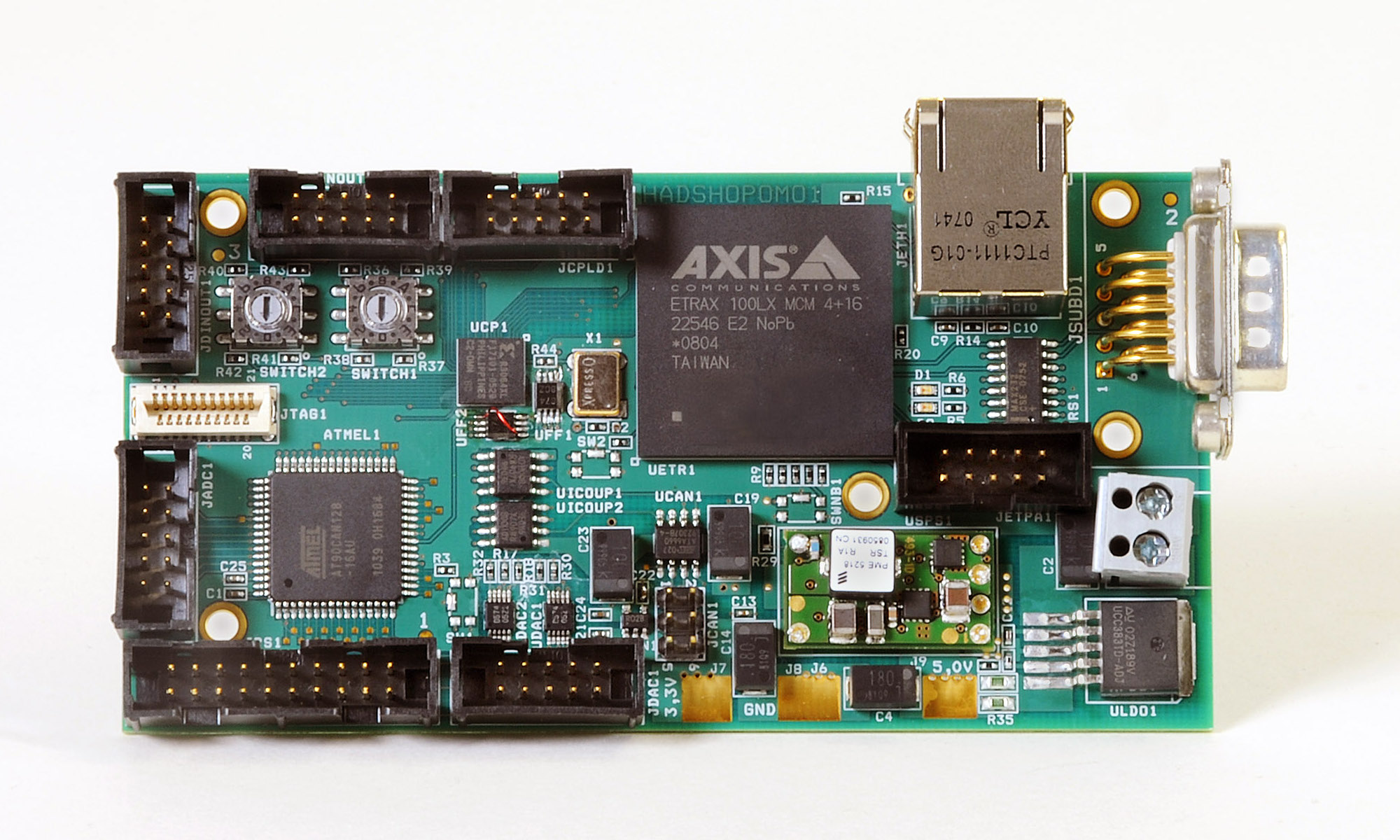

HadCon is a general purpose IO module for detector and experiment control as well as for small data acquisition systems. (HADControl general purpose board)

Since its first application has been a power monitor for the Hades Shower Detector it has been formerly introduced and well known as HadShoPoMo (Hades Shower Power Monitor (HADControl/HadShoPoMo general purpose board).

(HADControl general purpose board)

Since its first application has been a power monitor for the Hades Shower Detector it has been formerly introduced and well known as HadShoPoMo (Hades Shower Power Monitor (HADControl/HadShoPoMo general purpose board).HadCon has an SoC on-board, ETRAX 100LX MCM 4+16 from AXIS (Wikipedia: en/de) - which will be discontinued, see the new HadCon2. Running a standard Linux the Etrax provides "Connectivity to the world" via TCP/IP.

On the other side it connects via its internal serial interface to an ATMEL AT90CAN128 microcontroller and optionally to an Xilinx CPLD.

Via this junction the ATMEL provides a multitude of possible connections to field buses and general I/O ports. EPICS base and its applications, modules, and extensions can be cross-compiled to run on Etrax Axis' CRIS architecture (see section Architecture: ETRAX's CRIS by AXIS

- Summarizing:

- CPU: AXIS ETRAX 100LX MCM 4+16

- Microcontroller: ATMEL AT90CAN128

- I2C (internal)

- 2 × 4-channel 8-Bit DAC - Digital-to-Analog Converter

- CANbus

- galvanically isolated CAN - High-speed CAN Transceiver

- optional external power supply

- galvanically isolated CAN - High-speed CAN Transceiver

- SPI

- ADCs

- RS232

- 32 digital I/Os

- I2C (internal)

- CPLD: Xilinx XCR3064XL-6CS48C

- 2 × Rotary Code Switches, hexadecimal coding

- Ericsson PME 5218TS switching regulator for up to 6A 3.3V power usable for other boards

- full EPICS support

Documentation

Info

- GSI-EE's Documentation

Layout

Powering

- ≈≥ 6V (, < 5 W), 5.5V to 8 V.

- Ityp ≈ 200 mA

- internal power regulator

- Ericsson PME 5218TS switching regulator for up to 6A

- 3.3V power usable for other boards

- Ericsson PME 5218TS switching regulator for up to 6A

CPU

- Datasheets:

- User documentation:

- Kernel programming: formerly: Sergey Yurevic, HADES

- Documentation: HADES-wiki: How-to and resources

(local zip:EmbeddedLinuxDev...zip)

AND - setting HadCon to the right state

(local zip: EtraxMcmControl... .zip)

- Documentation: HADES-wiki: How-to and resources

Kernel

USART - Universal Synchronous and Asynchronous serial Receiver and Transmitter

| connects to | |

|---|---|

/dev/ttyS1 |

ATMEL |

/dev/ttyS0 |

RS232-connector |

Microcontroller

USART - Universal Synchronous and Asynchronous serial Receiver and Transmitter

| connects to | |

|---|---|

| USART0 | CPU |

CPLD (Complex Programmable Logic Devices)

- Xilinx 64 Macrocell CPLD (XC)R3064XL

connects to:

| Device* ↔ *Device | Bus/Signal | ||||

|---|---|---|---|---|---|

| pin | pins | ||||

| ETRAX | D0 |

CPLD | FB2 |

DATA |

|

D1 |

FB2 |

||||

D2 |

FB2 |

||||

D3 |

FB2 |

||||

A1 |

FB2 |

ADDR |

|||

A2 |

FB2 |

||||

A3 |

FB2 |

||||

A4 |

FB2 |

||||

| ATMEL | PC0 (A8) |

FB3 |

PC |

||

PC1 (A9) |

FB3 |

||||

PC2 (A10) |

FB3 |

||||

PC3 (A11) |

FB3 |

||||

PC4 (A12) |

FB3 |

||||

PC5 (A13) |

FB3 |

||||

PC6 (A14) |

FB3 |

||||

PC7 (A15/CLK0) |

FB3 |

||||

| JCPLD1 | 1 | FB4 |

CP_GP0 |

||

| 2 | FB4 |

CP_GP1 |

|||

| 3 | FB4 |

CP_GP2 |

|||

| 4 | FB4 |

CP_GP3 |

|||

| 5 | FB4 |

CP_GP4 |

|||

| 6 | FB4 |

CP_GP5 |

|||

| 7 | FB4 |

CP_GP6 |

|||

| 8 | FB4 |

CP_GP7 |

|||

I2C

-

Quad, 8-Bit, Low-Power, Voltage Output, I2C Interface Digital To Analog Converter, DAC5574, local copy

Quad, 8-Bit, Low-Power, Voltage Output, I2C Interface Digital To Analog Converter, DAC5574, local copy

- Addressing

Device I2 sub address Signals A1 A0 UDAC1: 4-channel DAC (DAC5574) 1 0 DACOUT1 ... DACOUT3UDAC2: 4-channel DAC (DAC5574) 0 1 DACOUT4 ... DACOUT7

2 × 4-channel 8-Bit DAC - Digital-to-Analog Converter

regulators

VIN 5.5 - 8V → linear regulator: 5V → switching regulator: 3.3Vlinear regulator VIN: 5.5V - 8V → VOUT: 5V

- Ericsson PME 5218TS

switching regulator: VOUT: 3.3V

galvanically isolated CAN-bus

Can - High-speed Can Transceiver

iCoupler Digital Isolator

Switches

- 2 ×

Rotary Code Switches, hexadecimal coding - P36SMT , local copy

Rotary Code Switches, hexadecimal coding - P36SMT , local copy

- pull ATMEL's

PC0...PC8down toGND

SWITCH1 Connector Pins AT90CAN128 via 4.7kΩ SWITCH2 Connector Pins AT90CAN128 via 4.7kΩ 1 PC0(A8)1 PC4(A12)2 PC1(A9)2 PC5(A13)4 PC2(A10)4 PC6(A14)8 PC3(A11)8 PC7(A15/CLK0)

Rotary Code Switches, hexadecimal coding

Buttons

SW1 |

not mounted |

SW2 |

not mounted |

SWNB1 |

not mounted |

LEDs

| pin | color | |

|---|---|---|

| ETRAX | PA6 |

??? |

PA7 |

??? |

Connectors

- I/O of ATMEL

JDINOUT1 Connector Pins AT90CAN128 JDINOUT2 Connector Pins AT90CAN128 1 PA0(AD0)1 PC0(A8)2 PA1(AD1)2 PC1(A9)3 PA2(AD2)3 PC2(A10)4 PA3(AD3)4 PC3(A11)5 PA4(AD4)5 PC4(A12)6 PA5(AD5)6 PC5(A13)7 PA6(AD6)7 PC6(A14)8 PA7(AD7)8 PC7(A15/CLK0)9/10 GND 9/10 GND

JDINOUT1 / JDINOUT2

- ADC inputs of ATMEL

Connector Pins AT90CAN128 comments 1 PF0(ADC0)2 PF1(ADC1)3 PF2(ADC2)4 PF3(ADC3)

5 PF4(ADC4)overlap with JTAG inputs of ATMEL 6 PF5(ADC5)7 PF6(ADC6)8 PF7(ADC7)

9/10 GND

JADC1

- JTAG connector

Connector Pins Signal comments 9/11 TCK10kΩ to V3_33 TDI← CPLD / Jumper J2 ← ATMEL 1 TMS7 TDO→ ATMEL (→ CPLD) 4/6/8/10/12 GND5 V3_32/13/14 not connected

JTAG1

- JCAN1 CAN connector

JCAN1 Connector Pins Signal comments 1 CANH↔ CAN - High-speed Can Transceiver ATA6660 ↔ iCoupler Digital Isolator ↔ ATMEL 2 CANL3/5 VCAN_INPUT4/6 GND_CAN

JCAN1

- Output of the 2 4-channel DAC (DAC5574)

Connector Pins Signal Device Device pin 1 DACOUT0UDAC1 VoutA2 DACOUT1VoutB3 DACOUT2VoutC4 DACOUT3VoutD5 DACOUT4UDAC2 VoutA6 DACOUT5VoutB7 DACOUT6VoutC8 DACOUT7VoutD9/10 GND

JDAC1

- mixed Signals DAC (DAC5574)

Connector Pins Signal Device comments 1/2 V5_0_CON3/4 GND5 DACOUT0UDAC1 VoutA6 DACOUT1VoutB7 DACOUT2VoutC8 DACOUT3VoutD9/10 POWER_ONAT90CAN128 PA7 (AD7)11 ADC0PF0 (ADC0)12 ADC1PF1 (ADC1)13 ADC2PF2 (ADC2)14 ADC3PF3 (ADC3)15 ADC4PF4 (ADC4)16 ADC5PF5 (ADC5)17 ADC6PF6 (ADC6)18 ADC7PF7 (ADC7)19/20 GND

JPS1

- RS232 connector Sub-D 9

Connector Pins ETRAX comments 2 RXD0ETRAX's /dev/tty0via RS232 driver3 TXD07 RTS08 CTS05 ==1/4/6/9 not connected

JSUBD1

Bugs, Notes, Remarks, Tweaks & Twiddling

- When driving 1-wire devices, typically via

JDINOUT2, make sure to have (at least) 1 pull-up resistor of about 3.3kΩ on the data line of the 1-wire bus connected to the powerVDD.- Recommended to have it at the master, e.g. at HadCon's connector

JDINOUT2. - Possible option for future, directly at the connector, when using one of

JDINOUT2'spins as permanent power pin.

- Recommended to have it at the master, e.g. at HadCon's connector

Notes and Remarks

1-wire

- Bridge Flip-flop to increase

ATMEL_CLOCKto 10MHz - to be able to transmit up to baud rates of 115200 you have to manipulate the hardware of the hadcon.

The clock signal of the oscillatorX1is 20 MHz. It is scaled down by two flip-flops (UFF1,UFF2) first to 10 MHz and then to 5 MHz.

Now 10 MHz are needed !

ThereforeUFF2has to be bridged or short-cut, i.e.- pin 5 of

UFF2has to be disconnected from its pad and removed - A cable has to be soldered connecting pin 1 of

UFF2to the solder pad of pin 5

- pin 5 of

Tweaks: increase ATMEL_CLOCK to 10MHz

-

SW2 -

SW2is not correct wired, don't use it

Bug: Switches

Firmware

Microcontroller

e.g. see:CPLD

-- PeterZumbruch - 16 Jul 2013

| I | Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

max232cse.pdf | manage | 395 K | 2011-06-15 - 13:54 | PeterZumbruch | MAX232CSE - 5V-Powered, Multichannel RS-232 Drivers/Receivers |

Please login to edit this topic

Topic revision: r10 - 2018-03-15, PeterZumbruch

- User Reference

- BeginnersStartHere

- EditingShorthand

- Macros

- MacrosQuickReference

- FormattedSearch

- QuerySearch

- DocumentGraphics

- SkinBrowser

- InstalledPlugins

- Admin Maintenance

- Reference Manual

- AdminToolsCategory

- InterWikis

- ManagingWebs

- SiteTools

- DefaultPreferences

- WebPreferences

- Categories

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)