You are here: GSI Wiki>Tasca Web>TascaControls>AutomaticRapidFillingAutomatus>ArfaFPGAVI (2009-11-09, TillKoch)

This VI is programmed in LV 8.6.1 and is designed to run on a PXI-7831R FPGA device.

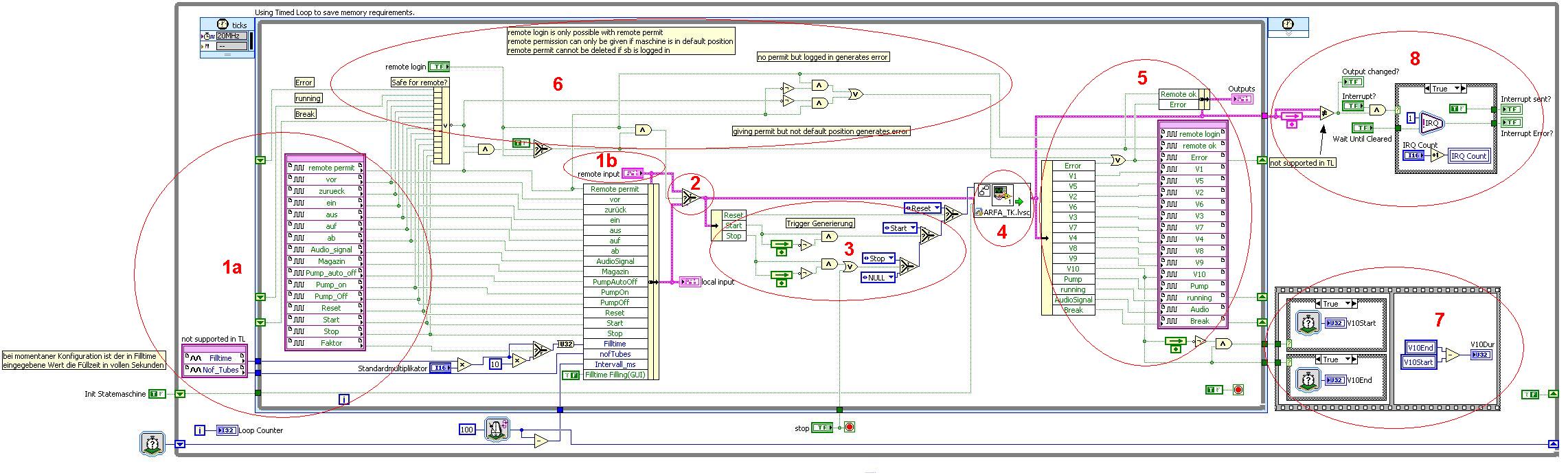

FPGA VI

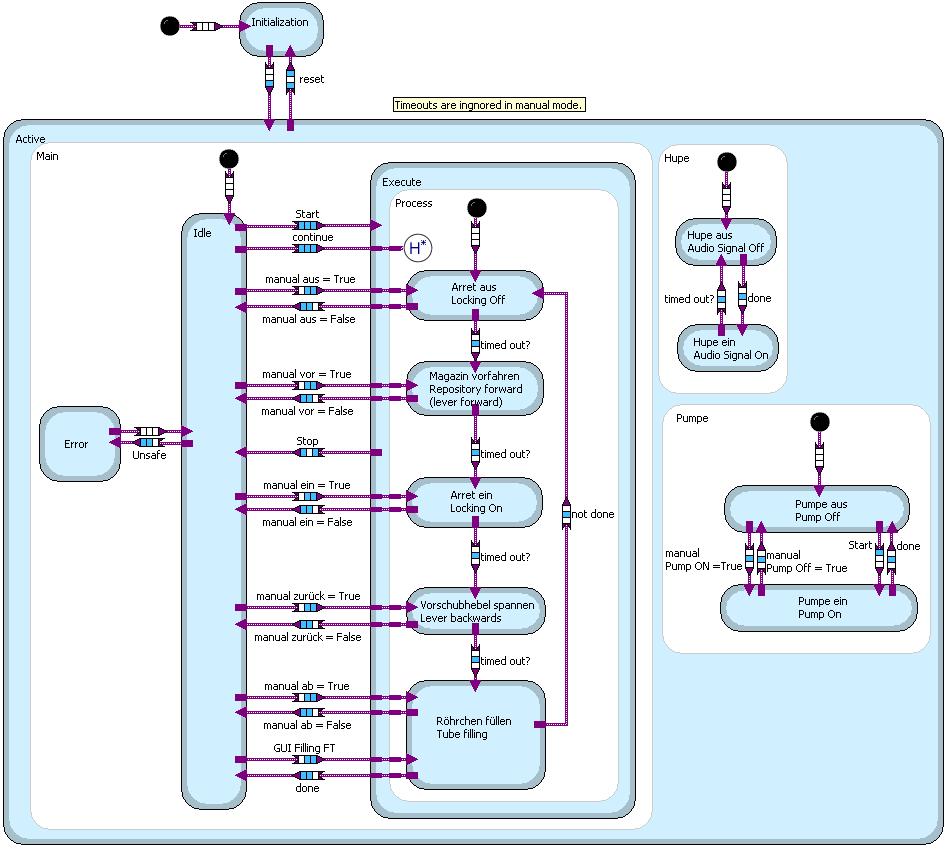

4 statemaschine

FPGA VI

1a read local inputs

The VI reads the current settings from the hardware case. The digital data is read inside the singel cycle timed loop(SCTL) to save memory requirements. The analog data is read outside the STCL because the STCL does not support read analog data.1b read remote inputs

The VI reads the inputs from the GUI at the HostVI,2 remote or local control?

The safety check decides which inputs will be led to the statemachine.3 trigger generation for the staemachine

Four triggers can be generated depending on the inputs:- NULL

- START

- starts the automized filling process with settings (filltime, number of tubes, repository side, audio signal, pump auto-off)

- STOP

- stops the automized filling process

- RESET

- makes new settings valid

4 statemaschine

- Initialisation

- take over settings to Statecharts' StateData

- Idle

- waits for "Start" trigger to start automized filling.

- waits for "Start" trigger to continue interrupted automized filling.

- waits for manual inputs

- vor (move the repository forward)

- zurück (move the lever backwards for next movement)

- ein (lock the repository so it is fixed if the lever moves backward)

- aus (unlock the repository so it moves forward if the lever moves forward)

- auf not in use

- ab (fill the current tube)

- waits for GUI inputs

- GUI Filling FT (activates filling for duration set at filltime) After pressing "Start (Filltime)"

- waits for unsafe action

-

- Execute

- executes the following steps,each after a set timeout of 100ms (response time of the valves), for n-times (n=number of tubes)

and returns to "Idle" when finshed- locking off

- lever forward

- locking on

- lever bachwards

- filling

- waits for "Stop" trigger to interrupt the automized filling.

- executes the following steps,each after a set timeout of 100ms (response time of the valves), for n-times (n=number of tubes)

- Hupe

- if automized filling is done and "Audio-Signal" was set, the "Audio Signal On"-State becomes active until timeout.

- Pumpe

- waits for manual input

- PumpOn (activates the pump)

- if automized filling is done and PumpAutoOff was set, the "Pump On"-State becomes active until timeout.

- waits for manual input

5 write outputs

The VI writes the outputs from the statemaschine to the FPGA outputs.6 safety check

This check is important to prevent interference between local and remote input.7 filltime check

This flat sequence structure counts the time valve nr. 10 is active and messures the real filltime.8 interrupt generation

The Host VI should only get active if there is a change at the FPGA outputs. This condition generates an interrupt and can activate the Host VI to process the data. -- TillKoch - 30 Oct 2009| I | Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

ARFAFPGAVI.JPG | manage | 273 K | 2009-10-30 - 16:50 | UnknownUser | ARFA FPGA VI |

| |

ARFAFPGAVImarked.JPG | manage | 299 K | 2009-10-30 - 17:01 | UnknownUser | ARFA FPGA VI with red circled regions |

| |

ARFAStatechartUnsafeTransition.JPG | manage | 47 K | 2009-11-03 - 14:35 | UnknownUser | ARFAStatechartUnsafeTransition |

| |

ARFAstatemachine.JPG | manage | 114 K | 2009-11-03 - 15:33 | UnknownUser | State Maschine at the FPGA VI for ARFA |

| |

FPGAVI.JPG | manage | 273 K | 2009-10-30 - 16:18 | UnknownUser | ARFA FPGA VI |

Please login to edit this topic

Topic revision: r3 - 2009-11-09, TillKoch

- User Reference

- BeginnersStartHere

- EditingShorthand

- Macros

- MacrosQuickReference

- FormattedSearch

- QuerySearch

- DocumentGraphics

- SkinBrowser

- InstalledPlugins

- Admin Maintenance

- Reference Manual

- AdminToolsCategory

- InterWikis

- ManagingWebs

- SiteTools

- DefaultPreferences

- WebPreferences

- Categories

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)