You are here: GSI Wiki>TOS/Timing Web>TimingSystemDocumentsNodes>TimingSystemNodesReleaseR1>TimingSystemNodesReleaseR1PEXARIA5 (2014-07-15, dbeck)

PEXARIA5 (Release R1)

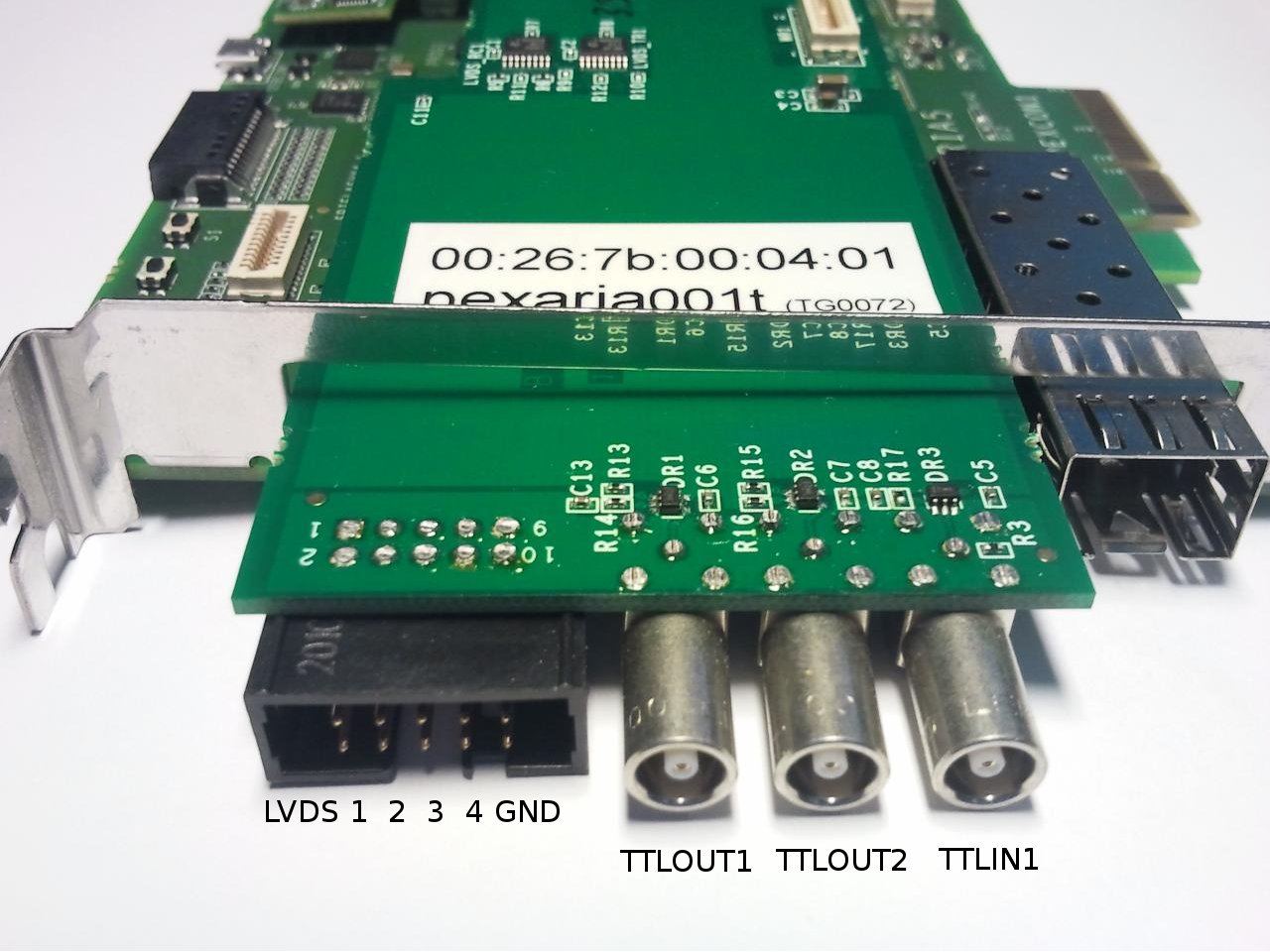

The PEXIARA5A is a PCIe carrier board based on an ArriaV FPGA. It can be White-Rabbit enabled using a WREX1 add-on board. I/O are implemented using a mezzanine board.Configuration 1

- Release Compatibility: R1

- Date: 15 October 2013

- Hardware:

- PEXARIA5 carrier board

- Black Cat mezzanine board

- WREX1 mezzanine board

- I/O Black Cat

- TTLIN1 : TLU trigger0

- TTLOUT1: ECA channel0 -> eca_gpio0

- TTLOUT2: ECA channel0 -> eca_gpio1

- LVDS1 : N/A

- LVDS2 : TLU trigger1

- LVDS3 : N/A

- LVDS4 : N/A

- I/O PEXARIA5

- LED5..8: ECA channel0 -> eca_gpio12..15

- PCIe: ECA channel1->pcie_slave_i

- Gateware and Firmware

- TLU

- triggers/fifos: 2

- fifo depth: 10

- ECA

- channels: 2

- condition table size: 128

- action queue length: 256

- Info

lxdv54:~> eb-info dev/wbm0 Project : pci_control Platform : pexaria5 +febex-ad6 +wrex1 Build type : developer preview Build date : Tue Oct 15 14:04:13 CEST 2013 Prepared by : Stefan Rauch <s.rauch@gsi.de> Perpared on : belpc098 OS version : Ubuntu 13.04, kernel 3.8.0-31-generic Quartus : Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version 082facc build: move common Makefile rules to shared build.mk file d638347 pexarria5: flash rx is locked slightly too close 8d3d19a arria phy: include disparity correction and arria5 800ps fix 35193fb build-id: integrate into all top files 0f52fa6 build-id: include platform information in all designs

- TLU

- Documentation

- pci_control.vhd: top file

- Issues

- stored information about the add-on board is not correct (can be obtained with eb-info)

- stored information about the eca channel 0 is not complete (can be obtained with eca-ctl)

Hardware

- Info by EE: Some figures and specs

-- DietrichBeck - 16 Oct 2013

-- DietrichBeck - 16 Oct 2013 | I | Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

pci_control.vhd | manage | 28 K | 2013-10-17 - 08:30 | UnknownUser | top file |

Please login to edit this topic

Topic revision: r16 - 2014-07-15, dbeck

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)