HADES RPC Threshold setting and Temperature/Voltage/Current Monitoring

1. Project status

- Initiation and Project-Definition

- Design in process

- Solution

- Thresholds:

- See the following (partially incomplete) documentation links

1.1. Status

2. Introduction

The large scale

HADES Experiment at GSI upgrades the new

RPC (resistive plate chamber) detector of

HADES.

The readout is based upon the

TRBv2: General Purpose Trigger and Readout Board ( )

)

Therefore the RPC setup requires control and monitoring elements to set and read two threshold settings for each RPC channel.

In addition 1-Wire

© bus based temperature sensors on DAQ boards have to be monitored.

These data are collected via the

AXIS' ETRAX FS chip on the TRBv2 board responsible for the DAQ. Since

EPICS can be run on ETRAX's cris architectures, EPICS will be used to provide this functionality.

As a further device the proposed

Low Voltage Supply Board's temperature, voltages and currents have to be monitored via the

ETRAX LX based

HADcon(trol) general purpose board module (a.k.a. HADShoPoMo).

2.1. System overview

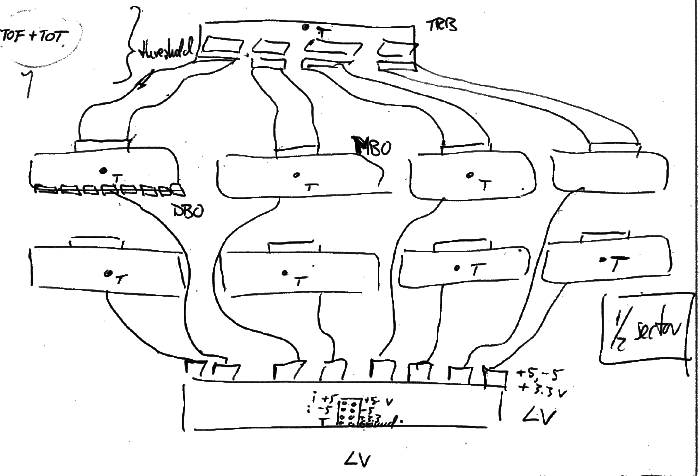

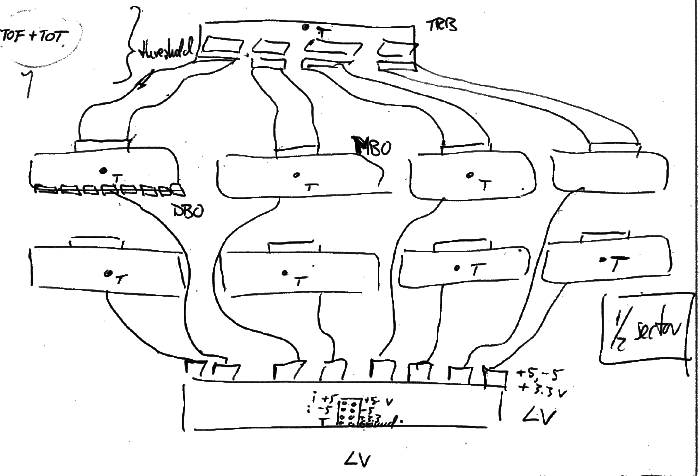

Picture 1 shows a sketched overview of the system of half a sector to be monitored and/or controlled.

|

| sketched overview of RPC (click on it to change size) |

|

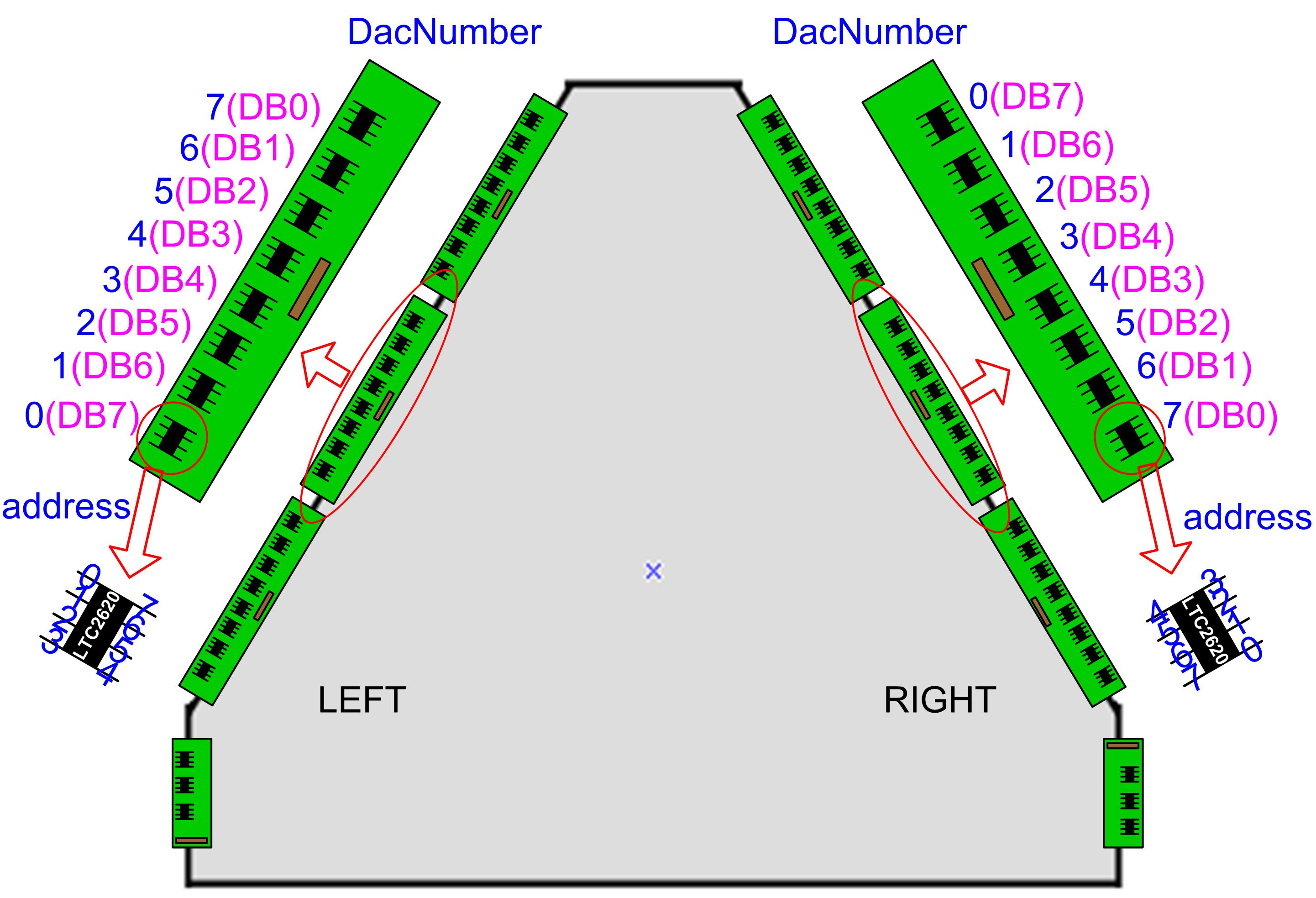

| Overview of one sector of the RPC wall (click on it to change size) |

2.2. Persons in charge:

- Alex Gil, HADES, IFIC (CSIC-University of Valencia)

- Elena Castro, HADES, Univ. Santiago

- Diego Gonzalez-Diaz, HADES, GSI

- Hardware and RPC support, Mapping Table (⇒ HADES Oracle Database)

- Juan Garzon, HADES, Univ. Santiago

- Peter Zumbruch, EE/KS, GSI

- Burkhard Kolb, HADES, GSI

- additional general EPICS support

2.3. Part I: TRB

One of the two tasks of this project is:

- to control and monitor via EPICS located on the ETRAX FS chip of the TRBv2:

- for each measuring channel on a daughterboard (DBO)

- TOF threshold (set)

- TOT threshold (set)

- for each motherboard (MBO)

- one temperature sensor (get)

- for each TRB board

- one temperature sensor (get)

| MBO temperatures total: 96 |

| TRB temperatures total: 24 |

| Totals |

| temperatures: |

|

thresholds: |

|

Total: |

|

| |

120 |

|

6144 |

|

6264 |

2.4. Part II: LV module

The other part faces the low voltage. Its task is

- to monitor via an attached general purpose board HADControl (aka HADSHOPOMO) which itself is based on an ETRAX LX100 chip and therefore also able to run EPICS on it:

- for each LV module

- currents of each output connector

- | Current of + 6 V (× 8 for each output connector -channel A of each ADC sensor-) | (get) |

- | Current of - 6 V (× 8 for each output connector -channel B of each ADC sensor-) | (get) |

- | Current of + 4 V (× 8 for each output connector -channel C of each ADC sensor-) | (get) |

- temperature

- one temperature sensor (get)

- dual switch

- shutdown (set)

- led status (set)

3. Interfaces

3.1.1. TRB Thresholds

3.1.2. TRB Temperature Reading

3.1.3. LV/HADControl Voltage/Current Reading

3.1.4. LV/HADControl Temperature Reading

4. Solutions

4.1. Hardware

4.2. Software

4.2.1. Base System

Since

EPICS can be run on ETRAX's cris architectures (q.v. above), EPICS will be used to provide the controls functionality.

4.2.2. Drivers / API

4.2.2.1. TRB Threshold Control

4.2.2.2. TRB Temperature Reading

4.2.2.3. LV/HADControl Voltage/Current Reading

4.2.2.4. LV/HADControl Temperature Reading

4.2.3. EPICS

4.2.3.1. Records

4.2.3.1.1. TRB Thresholds

4.2.3.1.2. TRB Temperature Reading

4.2.3.1.3. LV/HADControl Voltage/Current Reading

4.2.3.1.4. LV/HADControl Temperature Reading

5. Documentation

5.1. Software

5.1.1. Database Design

5.1.1.1. RPC Threshold settings

Using

VDCT (also a web-interface is available) those files document the database design for the

threshold settings. They are not (yet) used as templates for creating the database, but instead extracted from one existing set.

5.1.1.2. Functions from rpc_thr.c called in the sub records and their behavior

-

- (NOTE: if ToTL is part of some name then ToTR, ToFL and ToFR can replace it)

| sub record | Function | Action taken |

| stToTL | myStoreFcn | writes single values to one entry of the WRITE/PRESET table

- if not blocked by entry in FREEZE table

|

| defToTL | setDefaultToT

setDefaultToF | writes one value to every entry of the WRITE/PRESET table

- if not blocked by entry in FREEZE table

|

| sftToTL | setFreezeTable | sets a flag for each single channel in the FREEZE table if frozen or not, i.e. if access is allowed or not |

| retToTL | myRetrieveFcn | reads single entries from the READ table |

| gpToTL | readWriteTable | reads single entries from the WRITE/PRESET table |

| $(TRB):wT | myWriteFcn | writes the content of the WRITE/PRESET table to the device

and copies the content entry by entry to the READ table |

| $(TRB):readT | myReadoutFcn | reads/should read back the device's settings into the READ table |

5.1.2. RPC Threshold settings (rpc_thr.c and fs_fpga_int.c)

5.1.2.1. Functions:

- rpc_thr.c

-

spi_write(struct DataStreamS *dataStream, unsigned long offset, unsigned long mask, unsigned short mode, char *functionname)

-

read32_from_FPGA into readVal from device_address and offset

- clear/set bit in readVal by applying &= mask / |= mask

-

write32_from_FPGA readVal to device_address and offset

-

read32_from_FPGA into readVal2 from device_address and offset

- Error if readVal !!= readVal2

-

spi_clear

-

spi_set

-

write_one_bit_to_SPI

-

writing_Nbits_word_to_SPI (TYPE word, struct DataStreamS, unsigned int bits)

- split Nbits word of length bits, up into single bits starting from LSB

and loop bits times

- neg_slope

- write_one_bit_to_SPI

- pos_slope

-

writing_xyzWord_toSPI (unsigned int type, struct DataStreamS *my)

- depending on enum type (DONT_CARE_WORD, COMMAND_WORD, NO_COMMAND_WORD, ADDRESS_WORD, DATA_WORD)

- writing_Nbits_word_to_SPI (my→ element, bit size of element)

-

writing_whole_word ( struct DataStreamS *my)

- writing_xyzWord_toSPI(DONT_CARE_WORD, my)

- writing_xyzWord_toSPI(COMMAND_WORD, my)

- writing_xyzWord_toSPI(ADDRESS_WORD, my)

- writing_xyzWord_toSPI(DATA_WORD, my)

-

myWriteFcn(subRecord *precord)

- init_ports

- writing write Table to TRB's MBO SPI chain

- loop mbo

- loop _channel _

- negative_slope_CS

- loop dac

- set struct dataStream elements: mbo, dac, channel, data_word = thr (calibrated)

- writing_whole_word (dataStream)

- positive_slope_CS

5.2. Running & Usage

5.2.1. RPC Threshold settings

5.2.1.1. Running Etrax Thresholds Control

6. Administration

6.1. Minutes

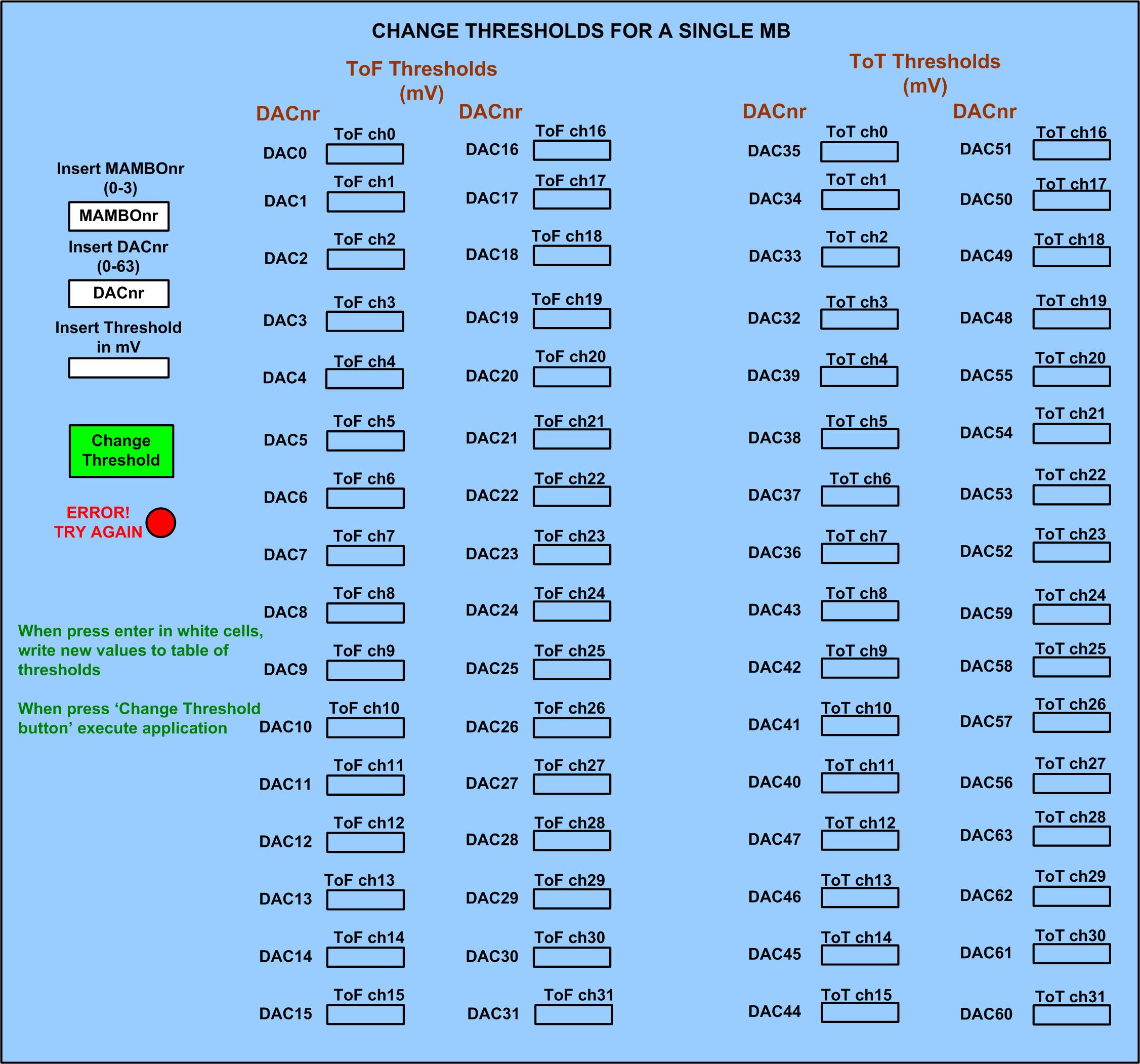

- Possible appearance of the slow control monitor:

|

| Possible appearance of the slow control monitor (click on it to change size) |

--

PeterZumbruch - 09 Jul 2008

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.