You are here: GSI Wiki>EPS Web>AdaptiveControlUnit>RelatedModuleDocuments>ICMHardwareTriplines (2018-09-27, DerekSchupp)

ICM Hardware Reißleinen

Das ICM besitzt insgesamt 4 HW Reißleinen.Jedes Interlock kann, je nach Typ, auf eine, zwei, drei oder alle diese Reißleinen konfiguriert werden.

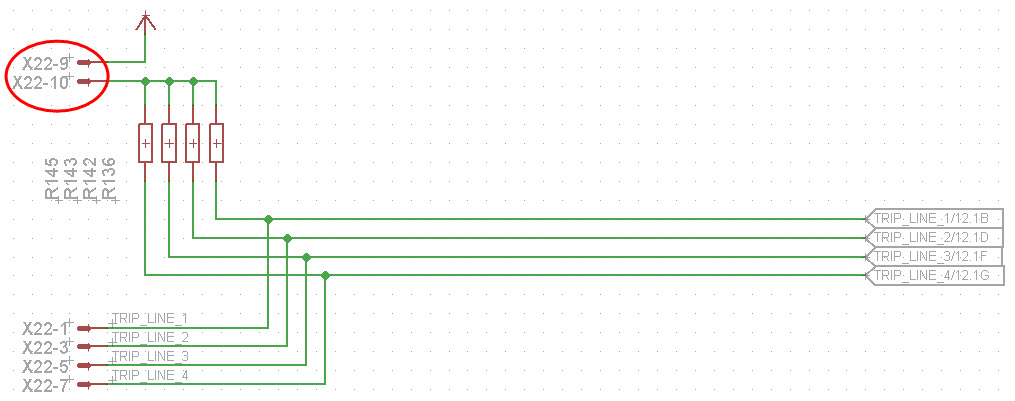

Nachfolgend ist beispielhaft ein elektrisches Interlock dargestellt, mit der Möglichkeit dieses auf alle 4 Reißleinen anbinden zu können.

Abbildung 1

Diese Reißleinen sind im OK Zustand ‚1‘.

Abbildung 1

Diese Reißleinen sind im OK Zustand ‚1‘.Das wird über Pullup-Widerstände (R136, R142, R143, R145) erreicht, die mittels eines Jumpers in X22 auf VCC gelegt werden.

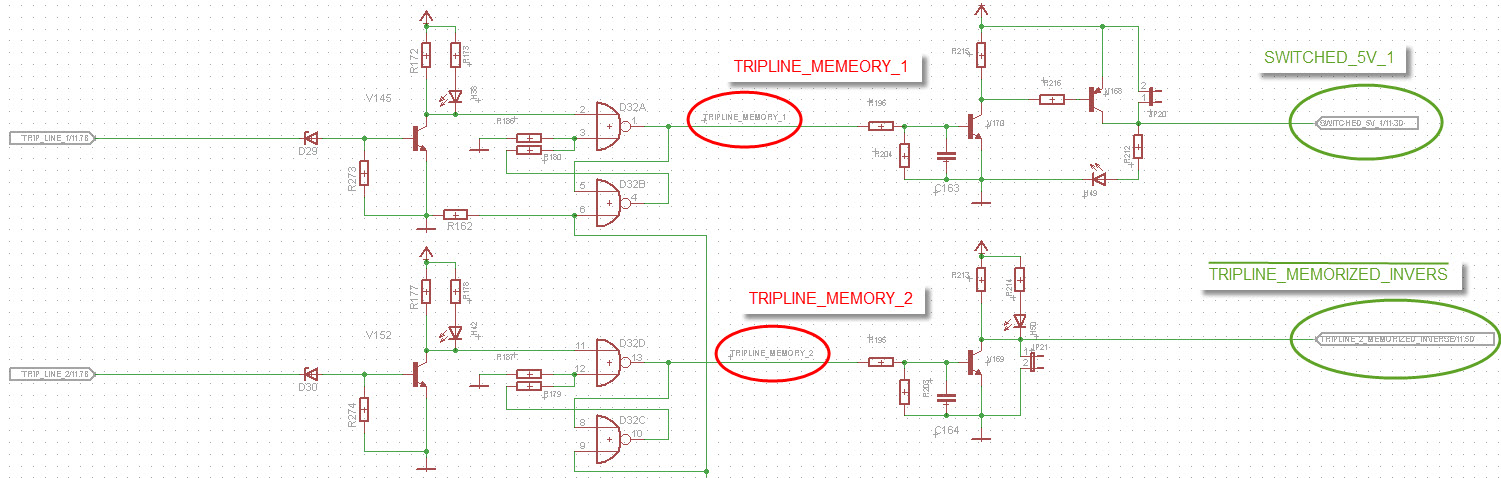

Abbildung 2

Wird nun ein Interlock ausgelöst, werden die zugeordneten Reißleinen dadurch auf GND gezogen. in der Hardware sind die Reißleinen 1 und 2 über Flip-Flops geführt, d.h.

Abbildung 2

Wird nun ein Interlock ausgelöst, werden die zugeordneten Reißleinen dadurch auf GND gezogen. in der Hardware sind die Reißleinen 1 und 2 über Flip-Flops geführt, d.h. die Zustandsänderung wird in der Hardware gespeichert, deren Zustand über zugehörige LEDs angezeigt. (grün= zugehörige Reißleine OK, nicht gezogen, aus =zugehörige Reißleine gezogen).

Abbildung 3

Die Reißleinen 3 und 4 hingegen werden nicht in der HW gespeichert, sondern deren Zustand nur über LEDs angezeigt.

Abbildung 3

Die Reißleinen 3 und 4 hingegen werden nicht in der HW gespeichert, sondern deren Zustand nur über LEDs angezeigt.

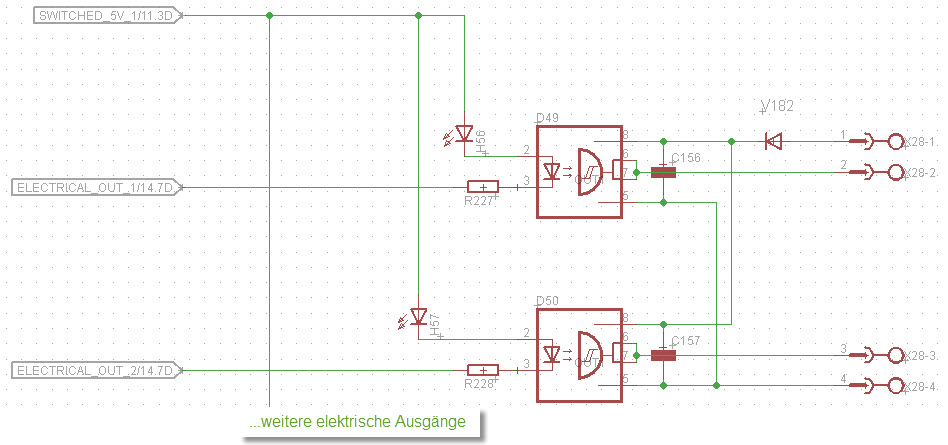

Abbildung 4

Der gespeicherte Zustand der Reißleinen 1 und 2 wird genutzt um Zusatzfunktionen in der Hardware durchzuführen. Das Signal von Reißleine 1 heißt „SWITCHED_5V_1“.

Abbildung 4

Der gespeicherte Zustand der Reißleinen 1 und 2 wird genutzt um Zusatzfunktionen in der Hardware durchzuführen. Das Signal von Reißleine 1 heißt „SWITCHED_5V_1“.Ist Reißleine 1 aktiv (also gezogen), werden mit diesem Aktiv-High-Signal die elektrischen Schaltausgänge des ICM dauerhaft deaktiviert.

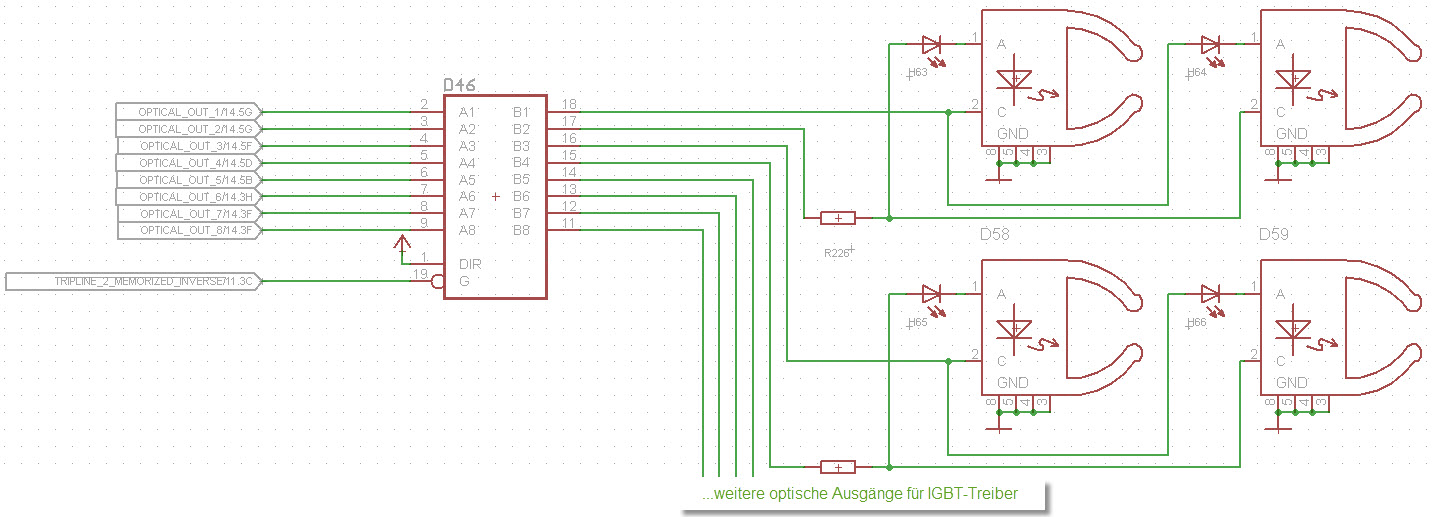

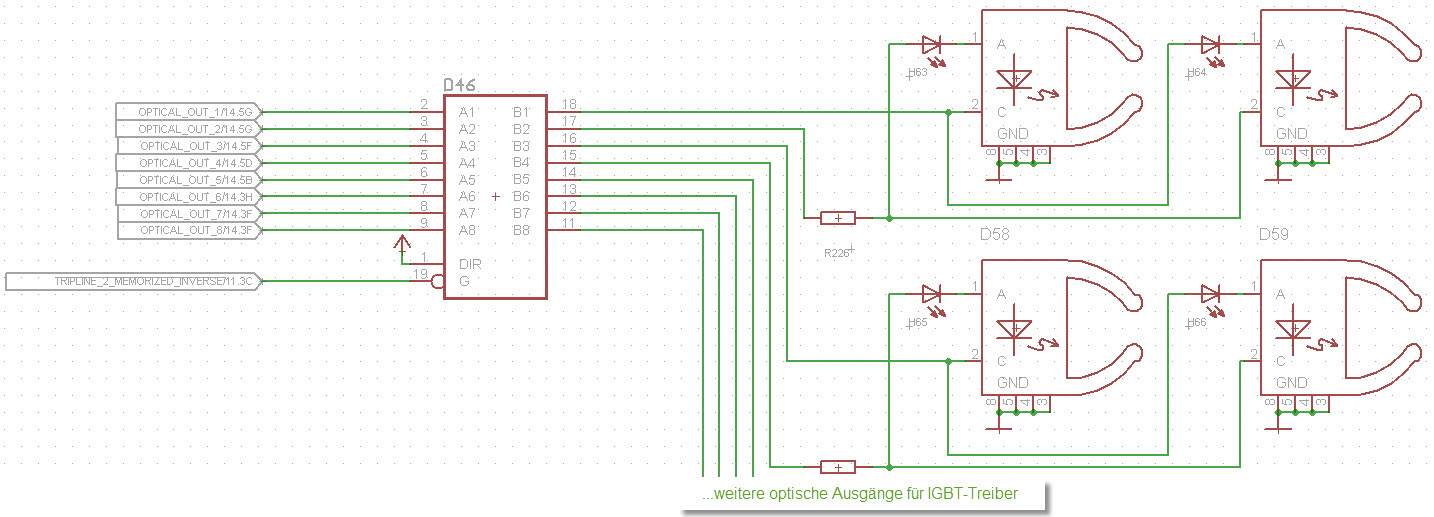

Abbildung 5

Das Signal von Reißleine 2 heißt „TRIPLINE_2_MEMORIZED_INVERSE“ und ist ein Aktiv-Low-Signal.

Abbildung 5

Das Signal von Reißleine 2 heißt „TRIPLINE_2_MEMORIZED_INVERSE“ und ist ein Aktiv-Low-Signal. Damit werden die Ausgangstreiber für die Steuerpulse der IGBT-Treiber dauerhaft gesperrt.

Abbildung 6

Beide Signale werden auch über X22 auf ein ggf. angeschlossenes Extension-Modul geleitet, um auch dort ggf. Ausgänge zu sperren.

Abbildung 6

Beide Signale werden auch über X22 auf ein ggf. angeschlossenes Extension-Modul geleitet, um auch dort ggf. Ausgänge zu sperren.

Abbildung 7

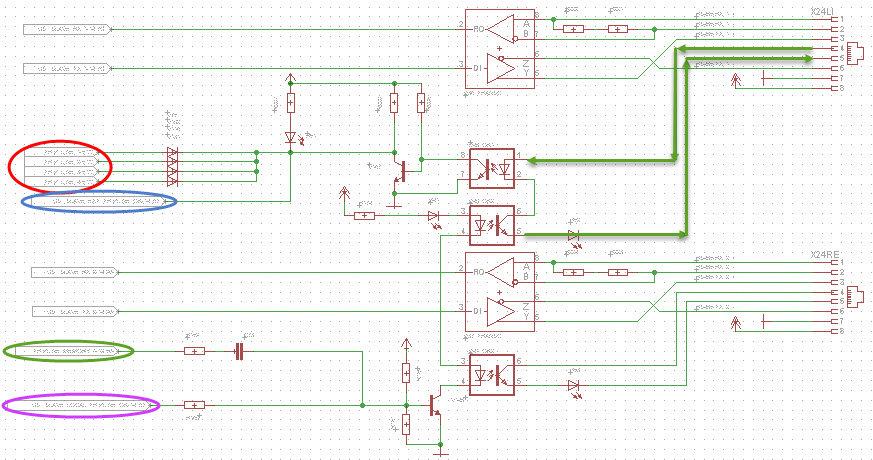

Alle 4 HW-Reißleinen (rot umrandet) können zusätzlich über die Summenreißleine (welche über die USI MFU ↔ Modulverbindung geführt ist) gezogen werden.

Abbildung 7

Alle 4 HW-Reißleinen (rot umrandet) können zusätzlich über die Summenreißleine (welche über die USI MFU ↔ Modulverbindung geführt ist) gezogen werden.

Abbildung 8

Das blau umrandete Signal „USI_SLAVE_EXT_TRIPLINE_OK“ führt zur FPGA-FW und gibt den Status der Summenreißleine an die FPGA-FW.

Die 4 HW-Reißleinen werden zwar auch als „TRIPLINE_MEMORY_[1..2]“ und „TRIPLINE_STATUS_[3..4]“ in der FPGA-FW erfasst, sorgen aber darüber nicht dafür, dass die Summenreißleine gezogen wird.

Das Ziehen der Summenreißleine erfolgt über das Signal „USI_SLAVE_LOCAL_TRIPLINE_OK“ (lila umrandet) und wird in der FPGA-FW erzeugt.

Abbildung 8

Das blau umrandete Signal „USI_SLAVE_EXT_TRIPLINE_OK“ führt zur FPGA-FW und gibt den Status der Summenreißleine an die FPGA-FW.

Die 4 HW-Reißleinen werden zwar auch als „TRIPLINE_MEMORY_[1..2]“ und „TRIPLINE_STATUS_[3..4]“ in der FPGA-FW erfasst, sorgen aber darüber nicht dafür, dass die Summenreißleine gezogen wird.

Das Ziehen der Summenreißleine erfolgt über das Signal „USI_SLAVE_LOCAL_TRIPLINE_OK“ (lila umrandet) und wird in der FPGA-FW erzeugt. Parallel dazu wird das Signal „TRIPLINE_MEMORY_1“ (grün umrandet) der ersten HW-Reißleine als Mechanismus zum Ziehen der Summenreißleitung genutzt. Problem Ist nun an X22 ein Opto-Extension-Modul angeschlossen, entfällt dadurch der Jumper um die 4 Pull-Up Widerstände für die HW-Reißleinen anzubinden.

Vielmehr werden die HW-Reißleinen auf das Opto-Extension-Modul weitergeleitet und dort mittels Pull-Up Widerstände angebunden. Wird nun das Opto-Extension-Modul abgezogen und keine Jumper auf X22 gesteckt tritt folgendes Szenario ein: Alle 4 HW-Reißleinen sind offen, d.h. die Signaleingänge „TRIP_LINE_[1..4]“ in den Abbildung 3 und Abbildung 4 sind nicht definiert an VCC oder GND gelegt.

Mit hoher Wahrscheinlichkeit werden die HW-Reißleinen als gezogen erkannt und dadurch die Signale „TRIPLINE_MEMORY_[1..2]“ und „TRIPLINE_STATUS_[3..4]“ = „0“.

Dieser Low-Zustand wird in der FPGA-FW aber nicht verarbeitet um die Summenreißleine über das in Abbildung 8 lila umrandete Signal „USI_SLAVE_LOCAL_TRIPLINE_OK“ auszulösen.

Dieses Signal wird aufgrund der vorherigen umstände also nicht „0“ werden. Dadurch kann auch das parallel angebundene Signal „TRIPLINE_MEMORY_1“ (grün umrandet) die Summenreisleine nicht auslösen. Sind alle anderen Interlockquellen fehlerfrei und wird eine System-Reset durchgeführt, wird die Summenreißleine nicht nur seitens der MFU, sondern auch des ICM freigegeben. Allerdings werden die elektrischen und optischen Ausgänge des ICM durch die HW-Reißleinen sicher gesperrt. Ein einschalten der SVE wäre also prinzipiell möglich, allerdings würde der Hauptschütz (am elektrischen Ausgang) nicht anziehen, was in eine Interlockmeldung resultiert.

Außerdem sind die optischen Ausgänge gesperrt und dadurch keine Steuerimpulse für die IGBT-treiber vorhanden. -- DerekSchupp - 2017-08-11

Please login to edit this topic

Topic revision: r6 - 2018-09-27, DerekSchupp

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)