You are here: GSI Wiki>EPS Web>AdaptiveControlUnit>HowThingsWork>ResponseTimeWithAnInterlock (2023-04-28, DerekSchupp)

Reaktionszeit eines Interlocks (ICM → MFU)

Wird am ICM ein Interlock ausgelöst, sorgt dies dafür, dass die daran angeschlossene(n) Reißleine(n) gezogen wird(werden). Eine gezogene Reißleine sperrt in der MFU den Regler und wird über die SCU an das Kontrollsystem gemeldet.Betrachtung anhand von Oszilioskopbildern

- Interlock kommt am ICM an

- nach ca. 14,8us (Reaktionszeit der Eingangsoptokoppler) wird dieses von der ICM Hardware erkannt, die an das Interlock angebundene(n) Reißleine(n) wird(werden) gezogen.

gelb = ICM Interlockeingang

blau = ICM Reißleine 2 - Die IGBT-Treiber des ICM werden sofort über zwei Mechanismen deaktiviert

- unmittelbar (ca. 320ns) durch die Firmware im FPGA

Sobald eine Reißleine auf dem ICM gezogen wird, schaltet das 'MultiSwitchingOperations'-Modul der ICM Firmware über das Signal 'USI_SLAVE_EXT_TRIPLINE_OK' unmittelbar das Signal 'SwitchingOperations_ControllerEnable' im ICM auf '0'.

Dadurch wird die PWM des ICM abgeschaltet.

gelb = ICM Reißleine 2

blau = IGBT-Treiber Ausgang.jpg)

- verzögert (ca. 42,2us) durch die Reißleine 2

Diese wirkt verzögert mit dem 'Tripline_2_Memorized_Inverse'-Signal auf das 'Enable' des hardwareseitigen Treiberbausteins.

gelb = ICM Reißleine 2

blau = 'nEnable' Eingang des hardwareseitigen Treiberbausteins.jpg)

- unmittelbar (ca. 320ns) durch die Firmware im FPGA

- Die gezogene Reißleine wird über 2 Wege an die MFU kommuniziert:

- als Statusinformation innerhalb der HighSpeed -Daten

- dies sorgt dafür, dass etwa 11,8us nach dem Ziehen der ICM-Reißleine, der/die Regler in der MFU gesperrt werden, weil das Signal 'ControllerEnable' auf '0' gesetzt wird.

gelb = ICM Reißleine

magenta = 'ControllerEnable'-Signal in der MFU

- dies sorgt dafür, dass etwa 11,8us nach dem Ziehen der ICM-Reißleine, der/die Regler in der MFU gesperrt werden, weil das Signal 'ControllerEnable' auf '0' gesetzt wird.

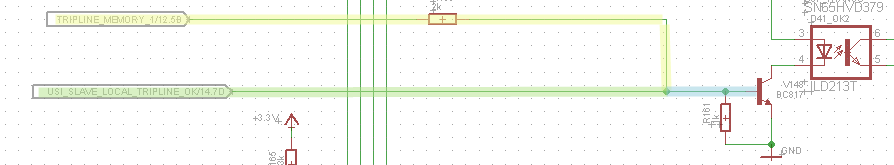

- via USI (RJ45) Kabel durch das Unterbrechen der darin befindlichen Hardware Reißleine

- dies sorgt dafür, dass etwa 24,2us nach dem Ziehen der ICM-Reißleine das Signal 'NoExtTripLinePulled' am 'Intr_In'-Eingang des SCU-BusSlave auf '1' gesetzt wird.

Damit wird diese Information an das Kontrollsystem gemeldet.

gelb = ICM Reißleine 1

blau= 'NoExtTripLinePulled'-Signal am 'Intr_In'-Eingang des SCU-BusSlave in der MFU

- dies sorgt dafür, dass etwa 24,2us nach dem Ziehen der ICM-Reißleine das Signal 'NoExtTripLinePulled' am 'Intr_In'-Eingang des SCU-BusSlave auf '1' gesetzt wird.

Schematische Darstellung

Die Erfassung des Interlocks wird über 2 Wege an die MFU kommuniziert.1. Hardwareseitige über die Reißleine, ausgelöst durch Tripline 1 → Tripline_Memorized_1 (~14,8µs + 24,2µs).

2. Über USI und damit über die digitiale Kommunikation (~14,4µs + 11,8µs). Mittels Tripline 2 werden die IGBT Trieber hardwareseitig etwa innerhlab von 14,2µs + 42,2µs deaktiviert.

Durch Abschalten der PWM aber schon nach etwa 14,2µs + 320ns.

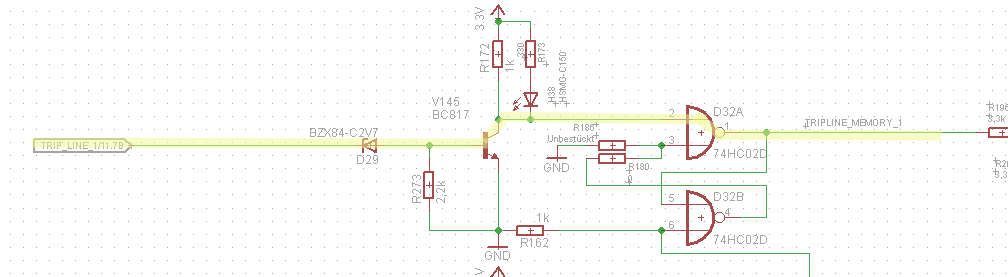

Realisierung in der Hardware

-- DerekSchupp - 2022-06-30

-- DerekSchupp - 2022-06-30 Please login to edit this topic

Topic revision: r6 - 2023-04-28, DerekSchupp

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)