You are here: GSI Wiki>EPS Web>AdaptiveControlUnit>HowThingsWork>InterlockDetectionInsideTheFPGA (2019-06-07, DerekSchupp)

Die Interlockerfassung im FPGA

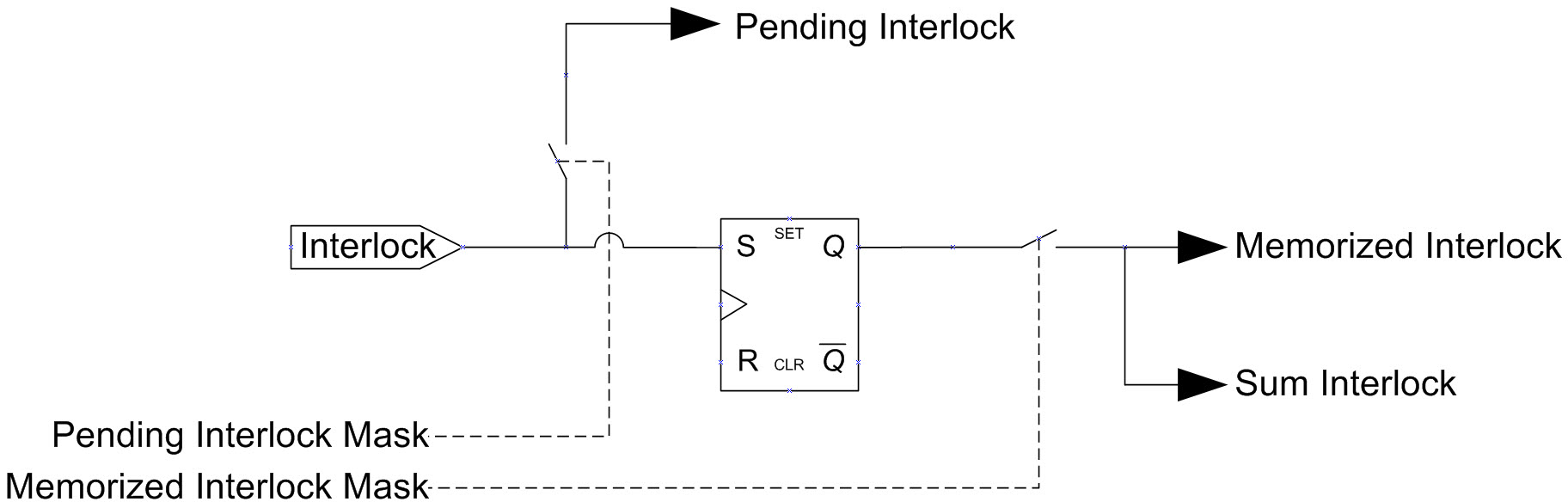

In der Regel werden Interlocks immer per Hardware auf dem entsprechenden Modul erfasst. Diese Hardwareerfassung soll die Reißleine betätigen. Die zusätzliche Erfassung der Interlocks im FPGA dient dazu Interlockinformationen an die MFU senden zu können. Dabei ist es möglich die FPGA interne Interlockerfassung durch den Nutzer zu beeinflussen. Jedes von der Hardware kommenden Interlocks wird über einen zugehörigen Schalter (MskP: capture pending interlock) als aktuell anstehendes Interlock und parallel dazu über ein Latch und einen weiteren Schalter (MskM: memorize pending interlock) als gespeichertes Interlock an die MFU übertragen. Abhängig von den Schalterstellungen ist es möglich diese Informationen für die MFU ein- oder auszumaskieren. Wichtig hierbei ist, dass die gespeicherten Interlocks diejenigen sind, die über das FPGA ebenfalls die Reißleine bedienen. Wird also bei einem Interlock die Speicherfunktion maskiert, wird dieses Interlock nicht die Summenreißleine bedienen. Das Zusammenspiel zwischen den aktuell anstehenden und den maskierten Interlocks in Bezug auf deren Konfiguration findet sich tabellarisch in MFUSoftwareChangeLog. Siehe dort MFU Nios Software Version 007.00003. -- DerekSchupp - 2019-06-07

-- DerekSchupp - 2019-06-07 Please login to edit this topic

Topic revision: r1 - 2019-06-07, DerekSchupp

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding GSI Wiki? Send feedback | Legal notice | Privacy Policy (german)