## On Time, in Style: Nanosecond Accuracy in Network Control Systems

Kreider, M.

#### Mathias Kreider Diplomingenieur (FH) Elektrotechnik

## On Time, in Style: Nanosecond Accuracy in Network Control Systems

**DOCTOR OF PHILOSOPHY**

COMPUTER SCIENCE

DIRECTOR OF STUDIES: Prof. Vic Grout

SUPERVISORS: Prof. John Davies Dr. Ralph Bär

Research was undertaken under the auspices of Glyndŵr University and GSI Helmholtzzentrum für Schwerionenforschung and was submitted in partial fulfilment for the award of a Degree of the University of Wales

### Thesis Declaration

I hereby declare that this work has not been accepted in substance for any degree and is not currently being submitted in candidature for any degree.

Date: 03/08/2017

This thesis is the result of my own investigations, except where otherwise stated. Other sources are acknowledged by references. A bibliography is appended.

Date: 03/08/2017

I hereby give consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

Date: 03/08/2017

The research was completed under the guidance of: Prof. Vic Grout (Director of Studies), Glyndŵr University.

Date: 03/08/2017

I didn't go to university. Didn't even finish A-levels. But I have sympathy for those who did.

– Terry Pratchett

#### **GLYNDŴR UNIVERSITY**

#### **Abstract**

Department of Computing

Doctor of Philosophy

On Time, in Style: Nanosecond Accuracy in Network Control Systems

by Mathias Kreider

The aim of this thesis is to prove it is possible to control and coordinate machines at sub-nanosecond accuracy. The demonstration case was the conceptualisation of a control system for large physics experiments, employing high precision timing technology and deterministic communication.

The results were empirically proven by means of a control system for a next generation particle accelerator, the Facility for Antiproton and Ion Research FAIR in Darmstadt, Germany. In the scope of this thesis, concepts and prototypes for both the control system's master unit, the *Data Master*, and the employed low latency network protocol, *Etherbone* were developed. In addition, a formal model of the control system was created. Its purpose is to guarantee deterministic operation by means of an offline analysis ahead of time, assaying latency bounds for a given set of commands.

This research shows that an alarm-based control system with a timing resolution of 1 ns is feasible. A scheme which allows machine schedules to be steered at runtime is presented and has been validated. Timely arrival can be guaranteed for trees of alternative command sequences, known ahead of time, as well as for limited changes during runtime. The proposed approach scales to several thousand controlled machines. It supports fully deterministic, parallel control processes that can utilise the full accuracy of the underlying time distribution system. The rate of control messages is only dependent on available network bandwidth.

The results of this work are already wholly in use at FAIR, controlling a real world particle accelerator. Etherbone components are also already in productive use at the European Centre for Nuclear Research CERN and other institutions, both for particle accelerator control systems and communication applications.

## Acknowledgements

Many thanks go to my supervisors, Vic Grout, for being ready to give good advice at all hours and making even the most tricky administrative trouble magically disappear, John Davies, for patiently editing out all my germanisms and always being a great host, and Ralph Bär, for giving me the chance to study beside my normal day job and especially for volunteering to become my supervisor when time was of the essence. My project advisor Dietrich Beck also has my sincere gratitude for his preparedness to read even my most cryptic drafts and discuss topics so far out of the box. I cannot thank you all enough for your continuous support and engagement.

My deepest thanks go to my family, especially my parents, Bärbel and Klaus, for their support and believing in me over the years it took me to write this thesis. The same goes for my future husband Markus, who was, despite being neither an engineer nor researcher, patiently listening to my ramblings about technology and maths he had never heard of before. You have my heartfelt respect for patiently working your way through all that, having nothing to gain from it than understanding my troubles and feeding your curiosity. Deep thanks also go to my brother Michael and my grandmother Ruth for proof reading and always listening to my nerdy ideas. Lastly I'd like to express my gratitude to my late grandfathers, Ludwig and Heinz, for trying to spark my interest in technology when I was but a child. It worked.

Many thanks go to my friends Daniel Fischer, whom I both hated and loved for giving the most hard-hitting feedback of them all, and Sabine Benda for proofreading. I also like to thank my colleagues from GSI for their ongoing support in creating this work. Thanks go to Stefan Rauch, for his readiness to talk ideas and being a universal trouble shooter, Marcus Zweig, for taming the White Rabbit and his dark sarcasm, Alexander Hahn, for his killer instinct and constructive feedback when testing the Data Master, Jiaoni Bai, for the hard numbers her dissertation provided and generally being a much nicer person than I could ever be, and finally Anjan Suresh, for implementing the continuous integration system which saved me such a lot of nerves.

Very special thanks go to my former colleague Wesley Terpstra, for his unconventional ideas, high standards, the enjoyable teamwork on elegant solutions and his both encouraging and brutally honest feedback. I'd also like to thank all the other colleagues from CERN and GSI who contributed to this work and their collaboration over all these years. My thanks also go to Steffen Bondorf and his colleagues at University of Kaiserslautern for the DiscoDNC Simulator and the associated productive exchange.

And finally, special thanks go to Ingo Stengel, the man who started this all by casually asking me at a Christmas party, more than six years ago, if I ever considered doing my PhD...

## **Contents**

| Tł | nesis | Declaration                               | ii |

|----|-------|-------------------------------------------|----|

| Al | bstra | c <b>t</b>                                | vi |

| A  | cknov | wledgements                               | i  |

| Ι  | Co    | ntext and Background                      | 1  |

| 1  | Intr  | roduction                                 | 3  |

|    | 1.1   | Motivation                                | 3  |

|    | 1.2   | Research Methodology                      | 3  |

|    | 1.3   | Contribution to Knowledge                 | 8  |

|    | 1.4   | Generalisation and Impact                 | 8  |

| 2  | Tim   | nekeeping                                 | 11 |

|    | 2.1   | Overview                                  | 11 |

|    | 2.2   | Timekeeping History                       | 13 |

|    | 2.3   | Time Systems                              | 16 |

|    | 2.4   | Oscillators and Clock Signals             | 17 |

|    | 2.5   | Digital Representations of Timestamps     | 22 |

|    | 2.6   | Time Distribution                         | 24 |

|    | 2.7   | Network Timing Services                   | 26 |

| 3  | Part  | ticle Accelerators                        | 33 |

|    | 3.1   | Overview                                  | 33 |

|    | 3.2   | Physics                                   | 33 |

|    | 3.3   | Types of Particle Accelerators            | 35 |

|    | 3.4   | Miscellaneous Components                  | 42 |

|    | 3.5   | Control Systems for Particle Accelerators | 43 |

| II | Pr    | roblem Analysis                           | 47 |

| 4  | FAI   | R Accelerator Case Study                  | 49 |

|    | 4.1   | Overview                                  | 49 |

|    | 4.2   | Control Systems                           | 50 |

|    | 4.3   | Beam Concept                              | 54 |

|    | 4.4   | Timing Constraints                        | 57 |

|    | 4.5   | Reliability                               | 60 |

|    | 4.6  | Summary of FAIR CS Requirements                                                                                                                                                                                                                                                                                                           | 2 |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 5  | Tech | anology Survey 6.                                                                                                                                                                                                                                                                                                                         | _ |

|    | 5.1  | Overview                                                                                                                                                                                                                                                                                                                                  | 5 |

|    | 5.2  | CPUs                                                                                                                                                                                                                                                                                                                                      | 5 |

|    | 5.3  | Hardware 6                                                                                                                                                                                                                                                                                                                                | 6 |

|    | 5.4  | Programmable Hardware                                                                                                                                                                                                                                                                                                                     | 7 |

| II | I A  | pproach and Implementation 75                                                                                                                                                                                                                                                                                                             | 5 |

| 6  | Ethe | erbone Protocol 7                                                                                                                                                                                                                                                                                                                         | 7 |

| Ŭ  | 6.1  | Overview                                                                                                                                                                                                                                                                                                                                  |   |

|    | 6.2  | Purpose and Environment                                                                                                                                                                                                                                                                                                                   |   |

|    | 6.3  | Requirements                                                                                                                                                                                                                                                                                                                              |   |

|    | 6.4  | Further Applications                                                                                                                                                                                                                                                                                                                      |   |

|    | 6.5  | Related Work                                                                                                                                                                                                                                                                                                                              |   |

|    | 6.6  | Architecture                                                                                                                                                                                                                                                                                                                              |   |

|    | 6.7  |                                                                                                                                                                                                                                                                                                                                           |   |

|    | 6.8  | 0                                                                                                                                                                                                                                                                                                                                         |   |

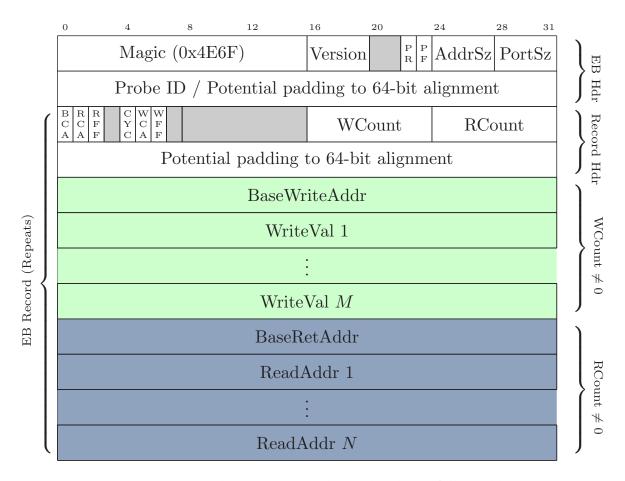

|    | 6.9  | Methods and Test Implementation85Etherbone Data Format8687878888898080808080818082808380848085808680878088808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080808080 <t< td=""><td></td></t<> |   |

|    | 0.9  | Etherbone Data Pormat                                                                                                                                                                                                                                                                                                                     | J |

| 7  | Data | a Master Hardware 9                                                                                                                                                                                                                                                                                                                       | 1 |

|    | 7.1  | Overview                                                                                                                                                                                                                                                                                                                                  | 1 |

|    | 7.2  | System on Chip Architecture                                                                                                                                                                                                                                                                                                               | 1 |

|    | 7.3  | Prototype Synthesis Analysis                                                                                                                                                                                                                                                                                                              | 2 |

|    | 7.4  | Message Priority Queue                                                                                                                                                                                                                                                                                                                    | 6 |

|    | 7.5  | Etherbone Master                                                                                                                                                                                                                                                                                                                          | 1 |

|    | 7.6  | Fast Input/Output Module                                                                                                                                                                                                                                                                                                                  | 5 |

| 8  | Data | Master Firmware 10                                                                                                                                                                                                                                                                                                                        | 9 |

|    | 8.1  | Overview                                                                                                                                                                                                                                                                                                                                  | 9 |

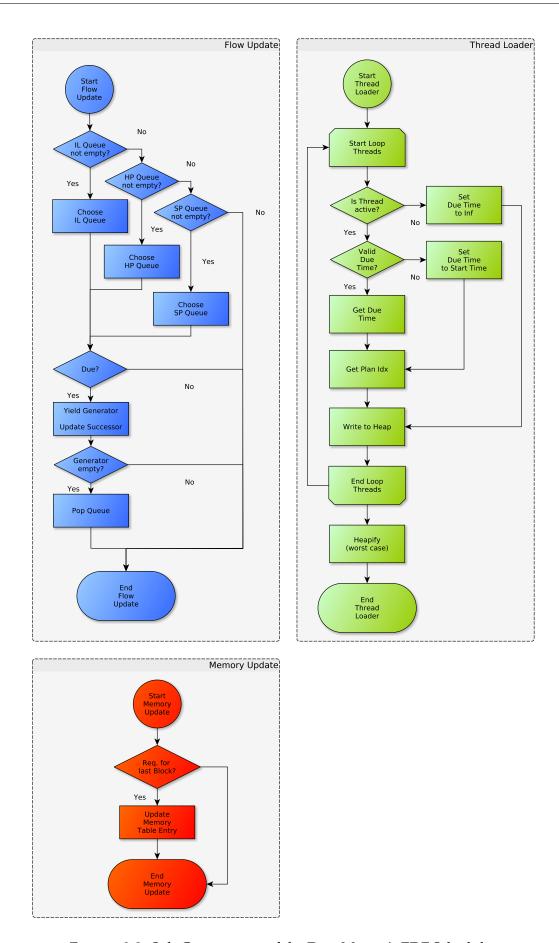

|    | 8.2  | Scheduler                                                                                                                                                                                                                                                                                                                                 | 9 |

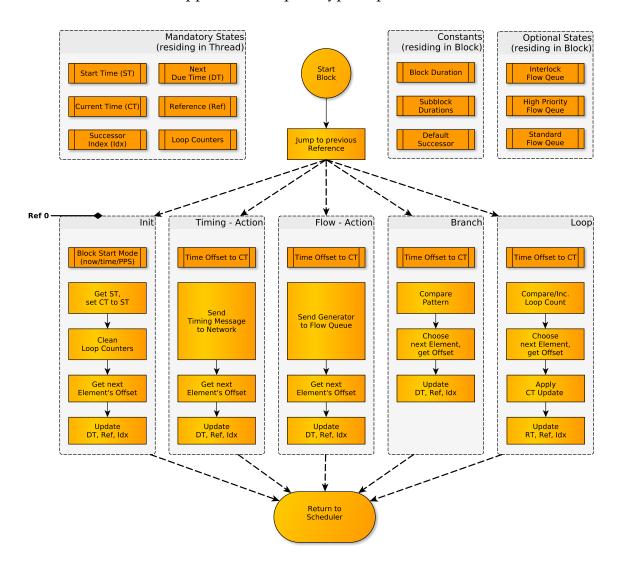

|    | 8.3  | Payload Programs                                                                                                                                                                                                                                                                                                                          | 6 |

|    | 8.4  | Memory Management                                                                                                                                                                                                                                                                                                                         | 7 |

|    | 8.5  | Considerations on RT Flow Control                                                                                                                                                                                                                                                                                                         | 2 |

|    | 8.6  | Deterministic Programming                                                                                                                                                                                                                                                                                                                 | 8 |

| 9  | The  | oretical Model 13                                                                                                                                                                                                                                                                                                                         | 7 |

|    | 9.1  | Overview                                                                                                                                                                                                                                                                                                                                  |   |

|    | 9.2  | Introduction to Network Calculus                                                                                                                                                                                                                                                                                                          |   |

|    | 9.3  | Approach for modelling the Data Master                                                                                                                                                                                                                                                                                                    |   |

|    | 9.4  | Scheduler Models                                                                                                                                                                                                                                                                                                                          |   |

|    | 9.5  | Etherbone Master – Framer                                                                                                                                                                                                                                                                                                                 |   |

|    | 9.6  | Etherbone Master – TX                                                                                                                                                                                                                                                                                                                     |   |

|    | 9.7  | Forward Error Correction                                                                                                                                                                                                                                                                                                                  |   |

|    | 9.8  | Etherbone Slave and Event-Condition-Action Unit                                                                                                                                                                                                                                                                                           |   |

|    | 7.0  | Enterone on the Event Condition retion of the                                                                                                                                                                                                                                                                                             | , |

|   | • | • |  |

|---|---|---|--|

| X | 1 | 1 |  |

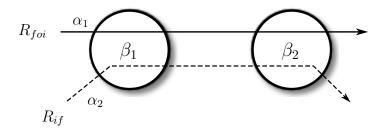

|    | 9.9 White Rabbit Network Model          | 169<br>170 |

|----|-----------------------------------------|------------|

| IV | V Conclusion                            | 183        |

| 10 | Evaluation                              | 185        |

|    | 10.1 Overview                           | 185        |

|    | 10.2 Test and Verification              | 185        |

|    | 10.3 Etherbone Analysis                 | 189        |

|    | 10.4 Network Calculus Simulation Models | 191        |

|    | 10.5 Observed Simulation Results        | 193        |

|    | 10.6 Full Test System Results           | 200        |

| 11 | Conclusion                              | 205        |

|    | 11.1 Overview                           | 205        |

|    | 11.2 Experimental Results               | 205        |

|    | 11.3 Real World Applications            | 206        |

|    | 11.4 Conclusion                         | 209        |

|    | 11.5 Outlook & Future Work              | 212        |

| Λ  | Source Code                             | 215        |

| А  | A.1 Data Master Gateware & Firmware     | 215        |

|    | 71.1 Data Master Gateware & Hilliware   | 210        |

| B  | <b>Employed Software</b>                | 217        |

|    | B.1 Programming Languages               | 217        |

|    | B.2 3rd Party Tools                     | 217        |

|    | B.3 Custom Inhouse Tools                | 218        |

| C  | Tables                                  | 219        |

|    | C.1 List of Publications                | 219        |

|    | C.2 Tables of Simulation Values         | 221        |

| Re | eferences                               | 227        |

# **List of Figures**

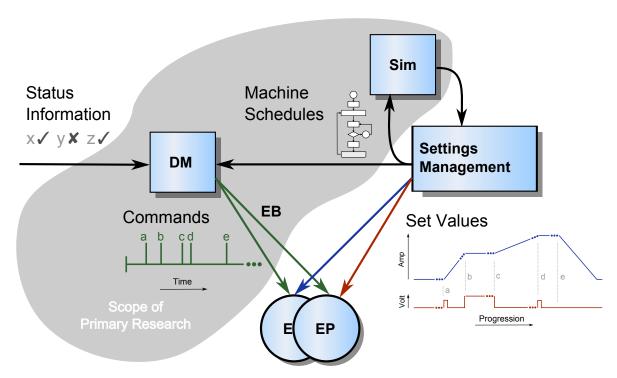

| 1.1 | Overview of realtime CS and Settings Management. Endpoints (EP) receive both commands and set values. Scope of Primary Research is shown in grey                                                 | 5          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

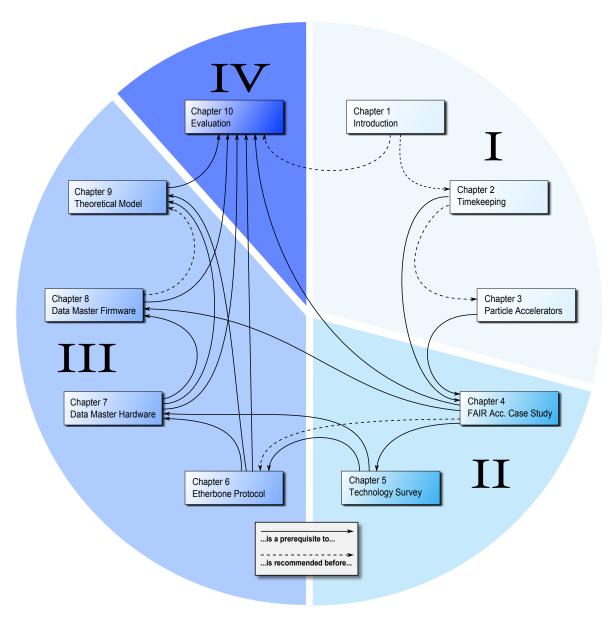

| 1.2 | Thesis Structure Coloured Slices indicate Parts, Arrows mark Dependencies between Chapters                                                                                                       | 9          |

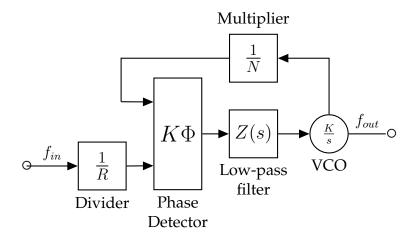

| 2.1 | Block diagram of a Phase-Locked Loop [31]                                                                                                                                                        | 21         |

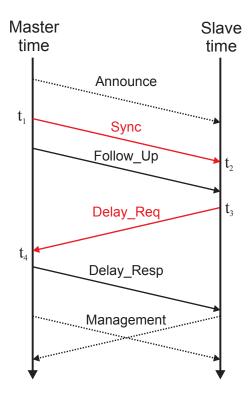

| 2.2 | Simplified PTP Synchronisation Handshake [42]                                                                                                                                                    | 28         |

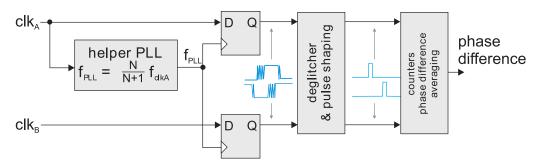

| 2.3 | White Rabbit Phase Measurement Hardware [42]                                                                                                                                                     | 30         |

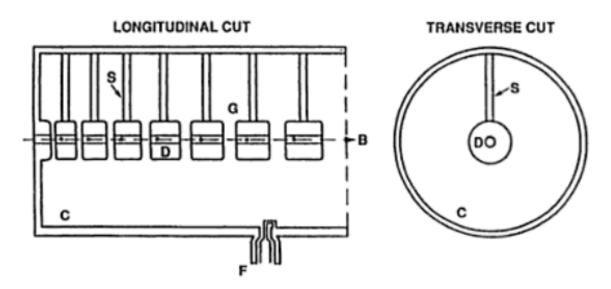

| 3.1 | Schematic of a drift tube linear accelerator based on the Alvarez design [49] <i>C</i> cavity, <i>S</i> struts, <i>D</i> tubes, <i>G</i> gaps, <i>F</i> RF input, <i>B</i> axis                  | 35         |

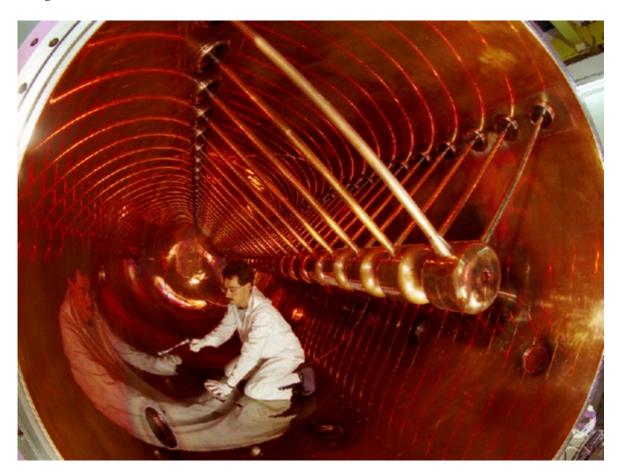

| 3.2 | Inside of an Alvarez tank at GSI. The drift tubes in the centre are supplied with the RF voltage by the diagonal struts. [52]                                                                    | 36         |

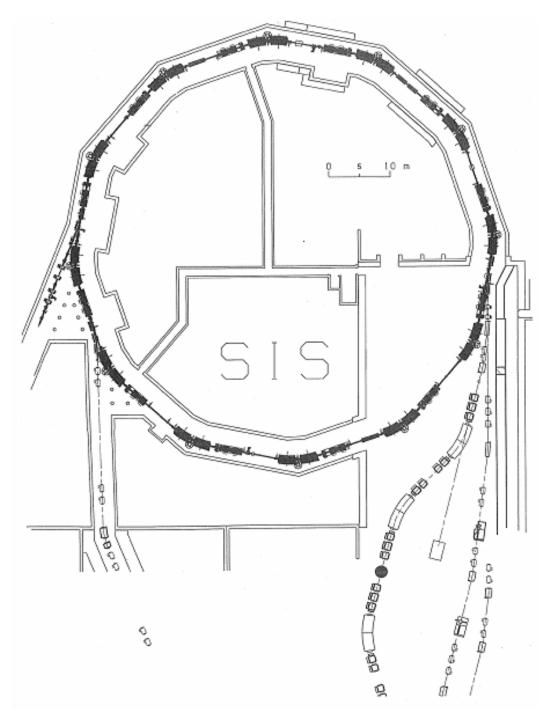

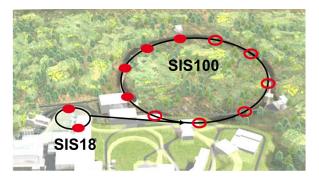

| 3.3 | Schematic of the SIS18 Heavy Ion Synchrotron at GSI. The SIS18 is built as a 12 sided polygon with an injection- (left), a re-injection- (second on left) and an extraction-channel (right) [54] | 38         |

| 3.4 | Synchrotron Components (SIS18) Front to back: RF acceleration section, yellow quadrupole focusing magnets, red dipole bending (corner) magnets [54]                                              | 39         |

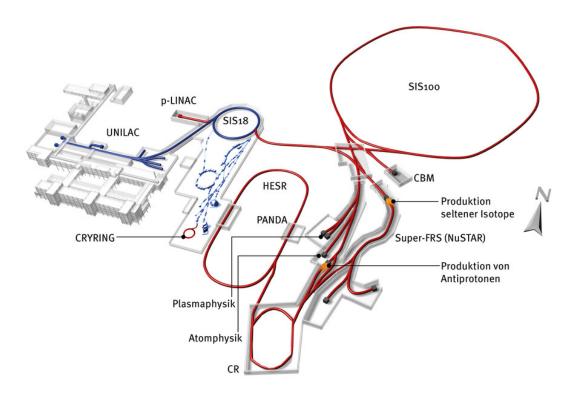

| 4.1 | GSI accelerator and future FAIR extension [57] Existing GSI facility in blue, planned FAIR machines in red                                                                                       | 49         |

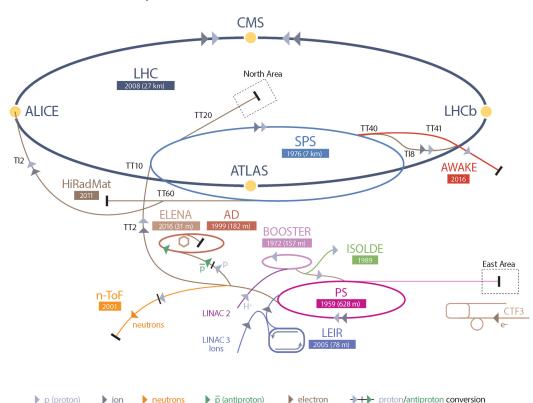

| 4.2 | Overview of CERN Accelerator Complex [65]. Rings are shown by labels with year of commissioning and circumference                                                                                | 52         |

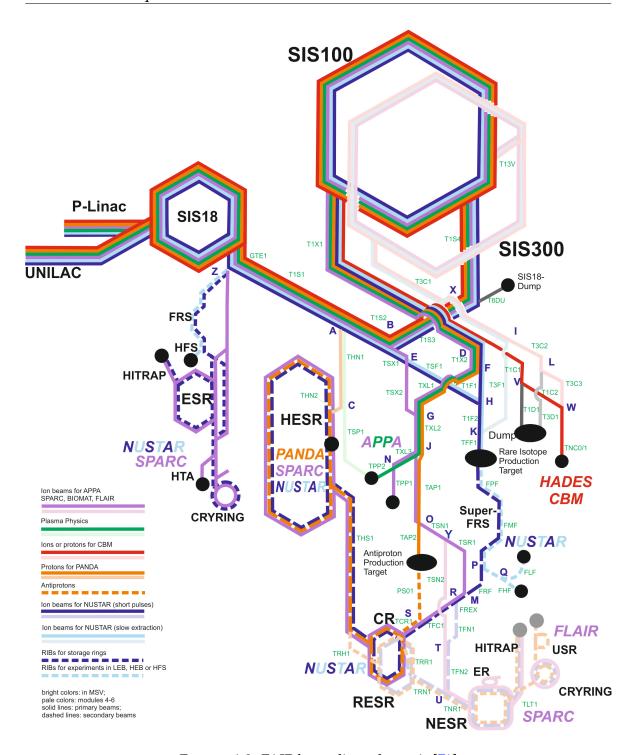

| 4.3 | FAIR beam-line schematic [71]                                                                                                                                                                    | 55         |

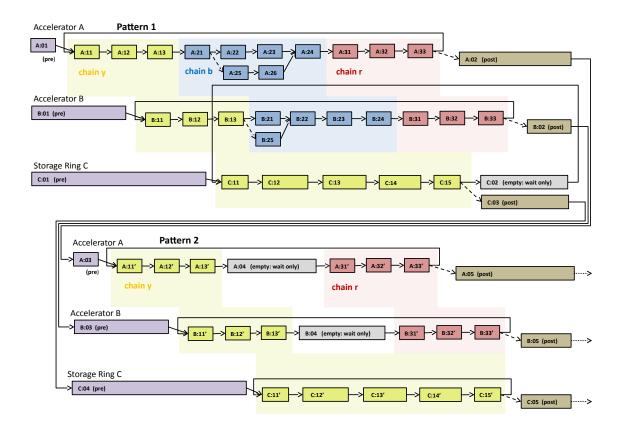

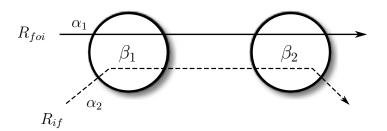

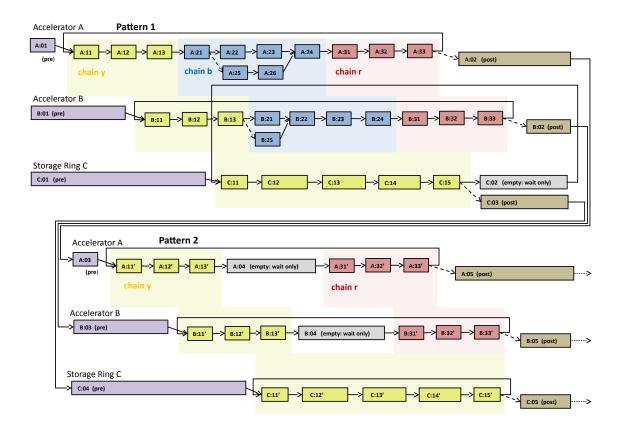

| 4.4 | Abstract view of BPCs, complete Pattern [71] Vertical Flow shows                                                                                                                                 | <b>F</b> ( |

| 4.5 | BPCs, horizontal shows Sequences                                                                                                                                                                 | 56<br>57   |

| 4.6 | Bunch-to-Bucket-Transfer [76]. Bunches are filled, Buckets are empty                                                                                                                             |            |

|     | circles                                                                                                                                                                                          | 58         |

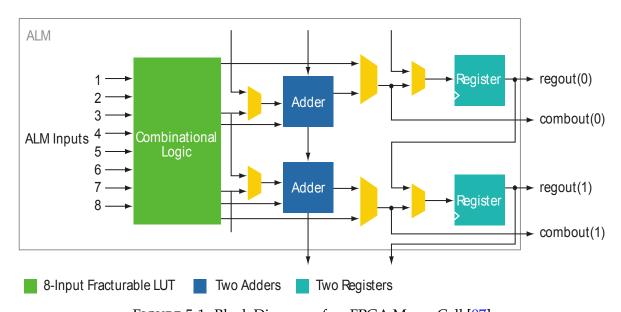

| 5.1 | Block Diagram of an FPGA Macro Cell [87]                                                                                                                                                         | 68         |

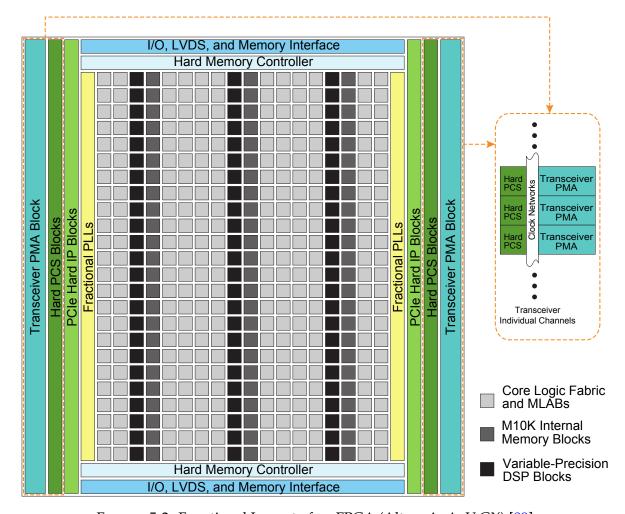

| 5.2 | Functional Layout of an FPGA (Altera Arria V GX) [89]                                                                                                                                            | 70         |

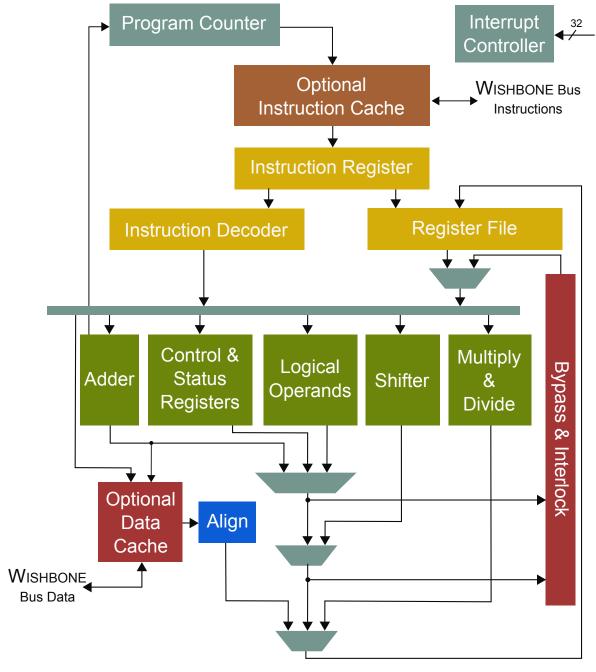

| 5.3 | Block Diagram of Lattice Mico 32 Soft CPU [91]                                                                                                                                                   | 72         |

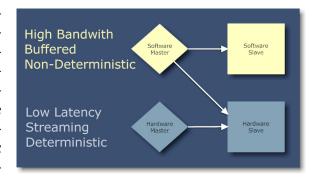

| 6.1 | Compatibility between EB node types                                                                                                                                                              | 80         |

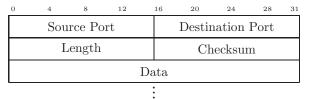

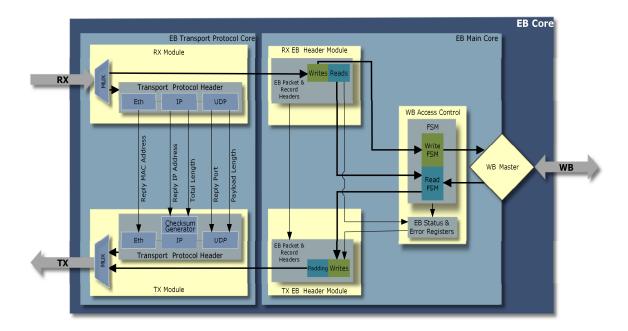

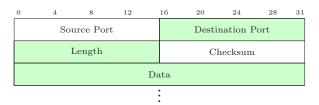

| 6.2 | Simplistic structure of the UDP Header                                                                                                                                                           | 81         |

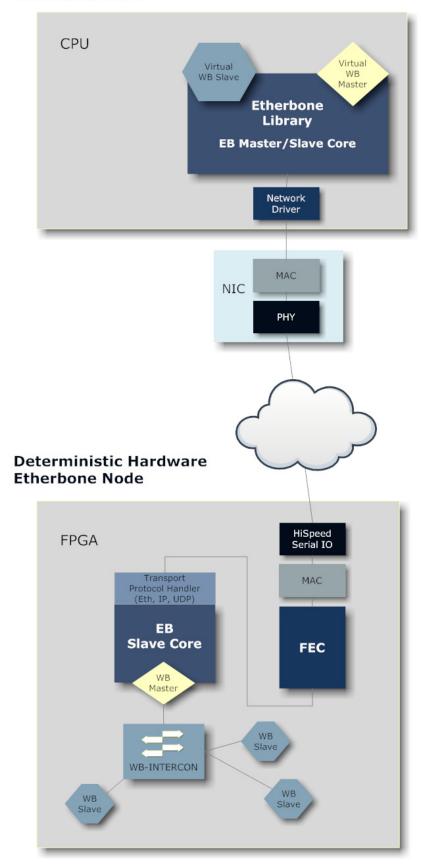

| 6.3 | PC EB master and FPGA based EB slave                                                                                                                                                             | 82         |

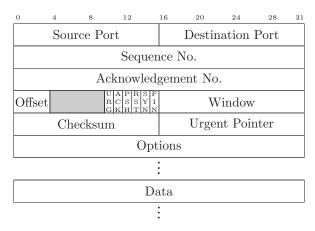

| 6.4 | TCP Header. More powerful, but more complicated                                                                                                                                                  | 83         |

| 6.5<br>6.6 | EB streaming hardware slave                                                                                             | 84       |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 0.0        | in green                                                                                                                | 84       |

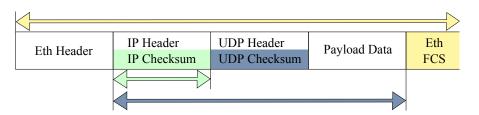

| 6.7        | Checksum coverage in a UDP/IP packet                                                                                    | 85       |

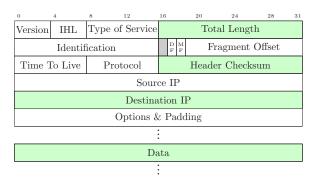

| 6.8        | IP Header, fields causing dependencies for the reply are marked in                                                      | 0.5      |

| 6.9        | green                                                                                                                   | 85<br>86 |

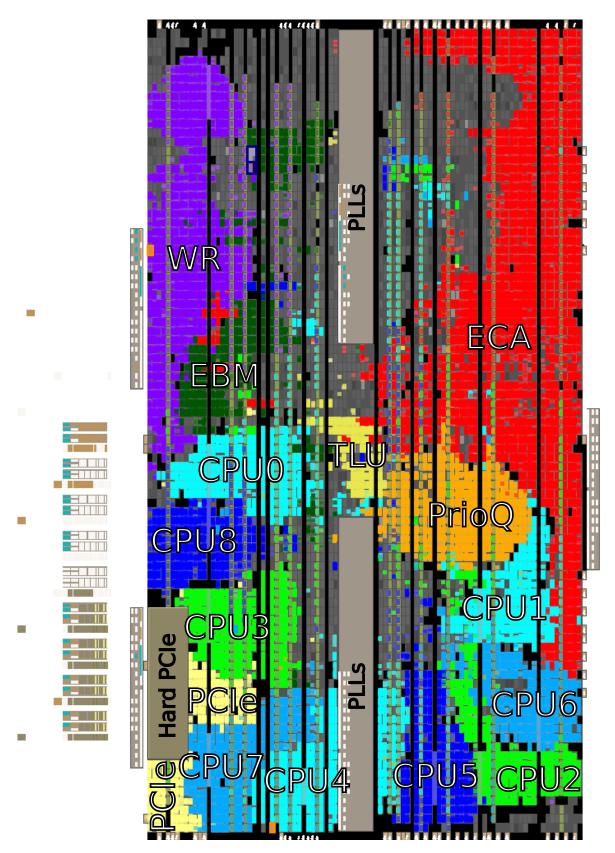

| 7.1        | Visualisation of Chip Usage with 9 CPU instances. More details are provided in the text                                 | 95       |

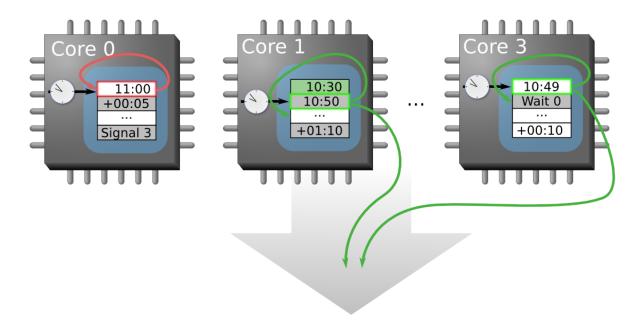

| 7.2        | Dispatch of Timing Messages in Soft-CPU Cluster [108]                                                                   | 96       |

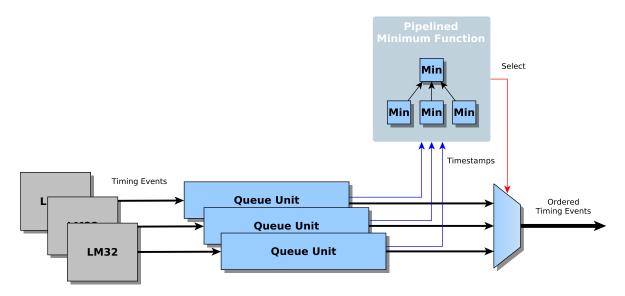

| 7.3        | Heap-based priority queue with Dual Port RAMs                                                                           | 97       |

| 7.4        | Overview of Priority Queue v3 Hardware                                                                                  | 99       |

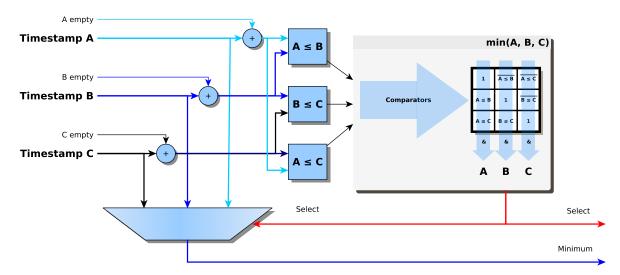

| 7.5        | 3-1 Minimum Function Hardware                                                                                           | 100      |

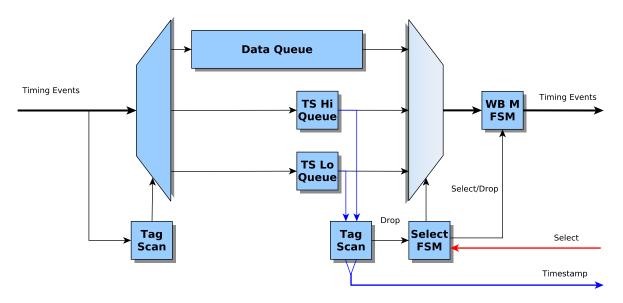

| 7.6        | Hardware Queue Unit with tag-based sorting                                                                              | 100      |

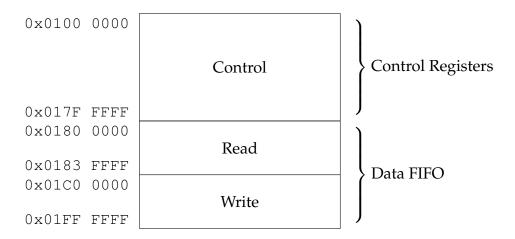

| 7.7        | Example Memory Map for EBM at 0x01000000                                                                                | 102      |

| 7.8        | Example Addr. Fields for EBM at 0x01000000 (10 high bits: 8b Dev.                                                       |          |

|            | Addr., 1b Control/Data, 1b Read/Write)                                                                                  | 103      |

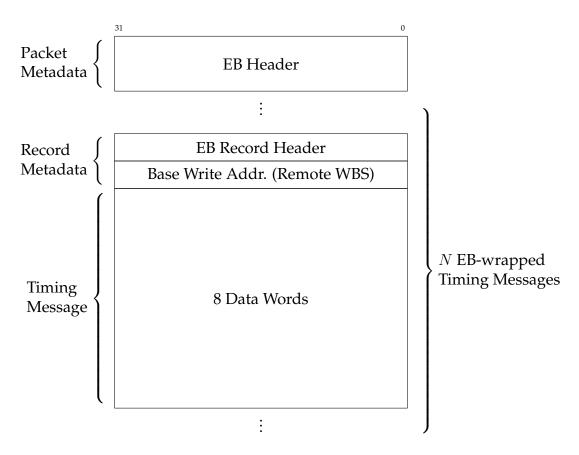

| 7.9        | EBM Output for Timing Messages                                                                                          | 104      |

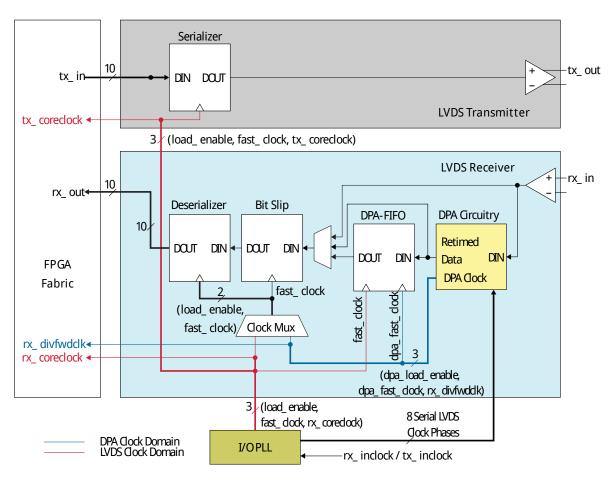

| 7.10       | Altera LVDS SERDES Channel [111]                                                                                        | 107      |

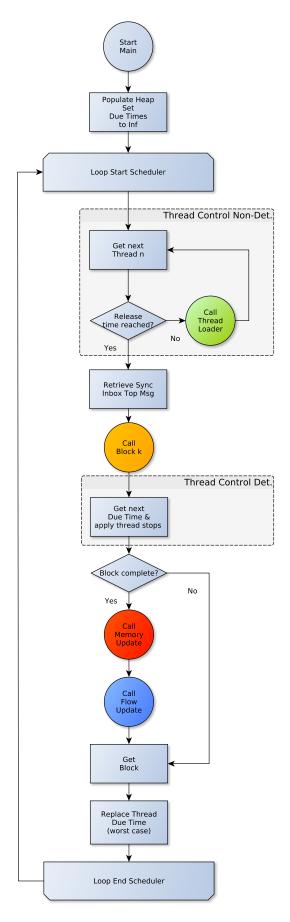

| 8.1        | The Data Master's EDF Scheduler                                                                                         | 110      |

| 8.2        | Sub-Components of the Data Master's EDF Scheduler                                                                       | 113      |

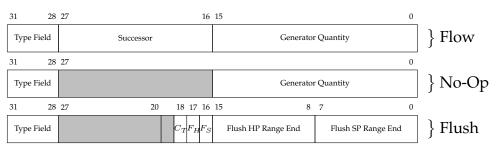

| 8.3        | DM Payload Program Structure                                                                                            | 116      |

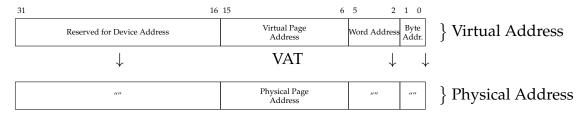

| 8.4        | Virtual Address Translation                                                                                             | 121      |

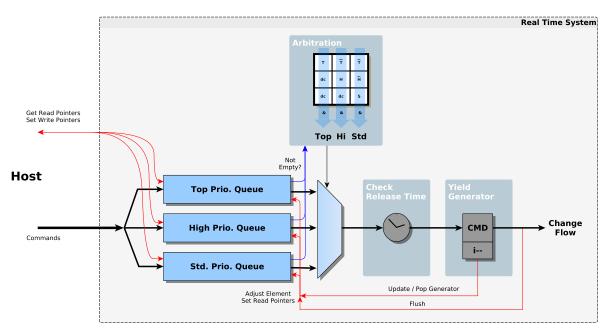

| 8.5        | CMD-Q Layout: Three prioritised generator queues, time aware, partial/complete flush                                    | 126      |

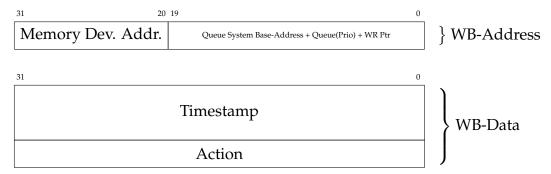

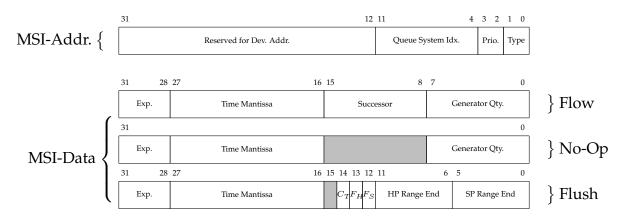

| 8.6        | DM Command Message                                                                                                      | 127      |

| 8.7        | Possible Actions for DM Command Messages                                                                                | 127      |

| 8.8        | Alternative Short-Hand for current MSI System                                                                           | 128      |

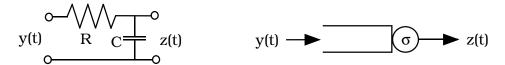

| 9.1        | Equivalency: System Theory Low-Pass and NC Shaper [123]                                                                 | 139      |

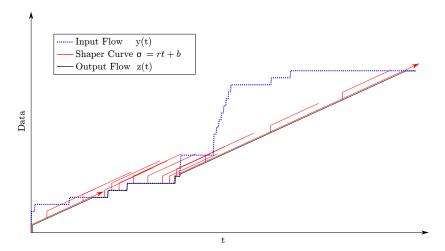

| 9.2        | Flow passing through a Shaper                                                                                           | 139      |

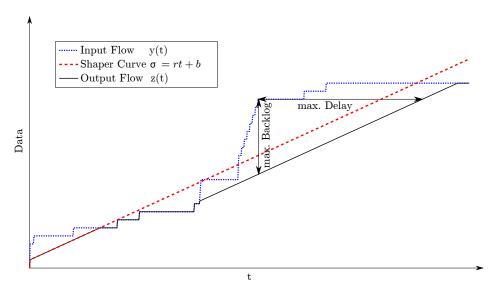

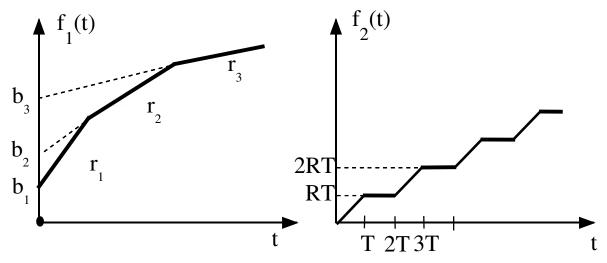

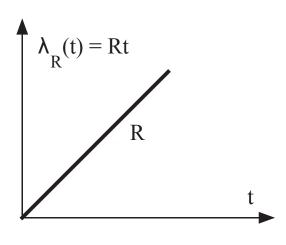

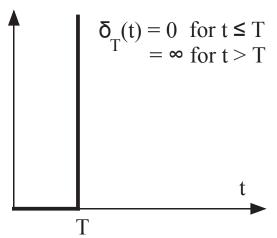

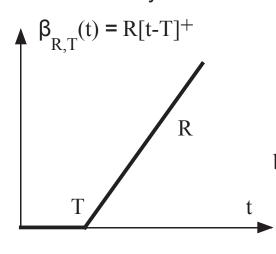

| 9.3        | NC Examples                                                                                                             | 140      |

| 9.4        | Examples of piecewise-linear Functions [123]                                                                            | 143      |

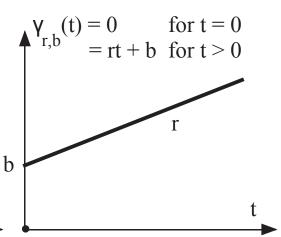

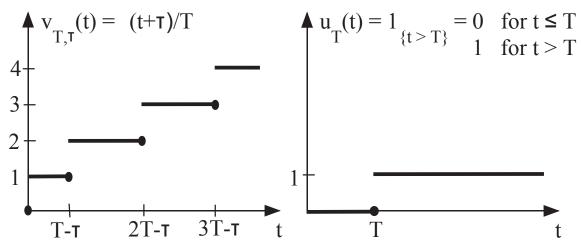

| 9.5        | Catalogue of commonly used Curve Functions in NC [123]                                                                  | 144      |

| 9.6        | Visualisation of the Effect of min-plus Convolution: Shaping curve                                                      |          |

| 0.5        | $\sigma$ is enforced at every point of input flow $y(t)$                                                                | 145      |

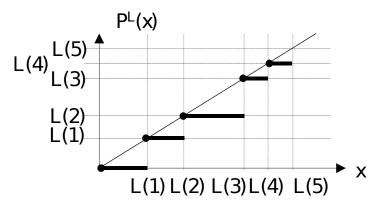

| 9.7        | Definition of Function $P^L$ [123]                                                                                      | 146      |

| 9.8        | Minimal Network Example: 2 Nodes, 2 Flows                                                                               | 149      |

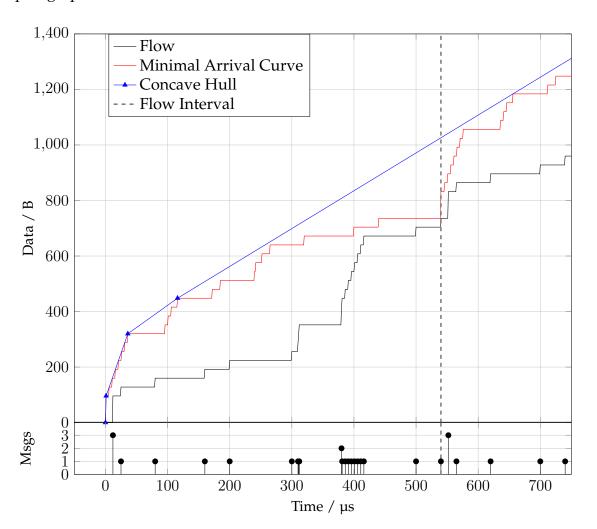

| 9.10       | Generation of a piece-wise affine Arrival Curve from Flow. The corresponding Messages are shown in the stem plot below. | 153      |

| 9.11       | responding Messages are shown in the stem plot below                                                                    | 153      |

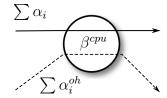

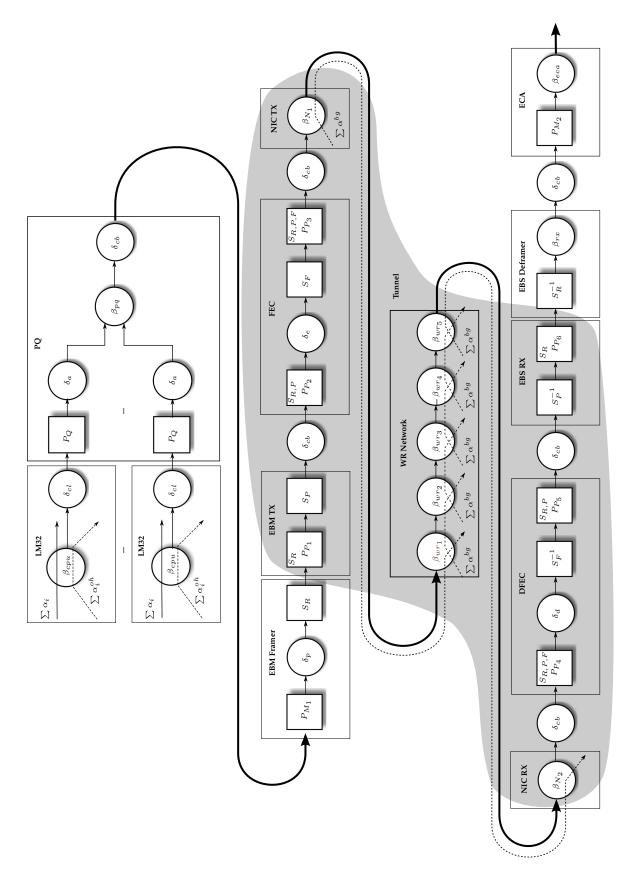

| 9.12       | PQ Scheduler node                                                                                                       | 160      |

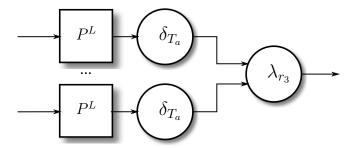

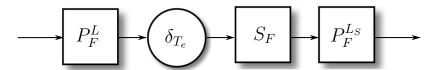

| 9.13       | Block Diagram of EBM Framer Module                                                                                      | 162      |

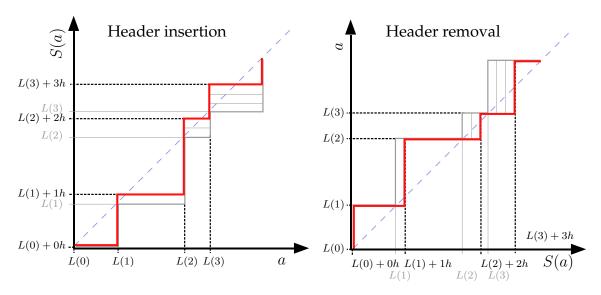

| 9.14       | Packet Header Scaling Functions                                                                                         | 164      |

|            |                                                                                                                         |          |

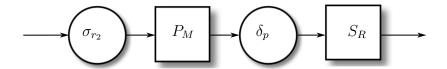

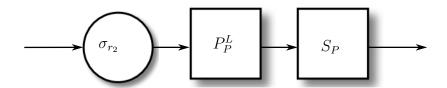

| 9.15         | Block Diagram of EBM TX Module                                                                                                                                                                                                                      | 166        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 9.16         | Block Diagram of FEC Module                                                                                                                                                                                                                         | 167        |

| 9.17         | Block Diagram of the DFEC Module                                                                                                                                                                                                                    | 168        |

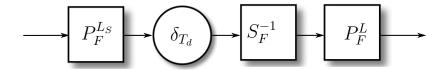

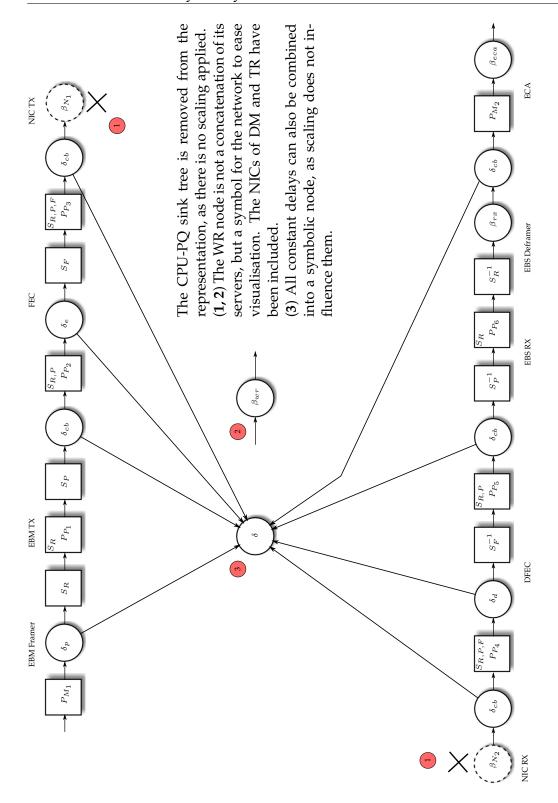

| 9.18         | Block Diagram of NC Control System Model: Data Master (1st and 2nd row), White Rabbit Network (3rd row), Timing Receiver (4th                                                                                                                       |            |

|              | row). Tunnel coverage is shown in grey                                                                                                                                                                                                              | 172        |

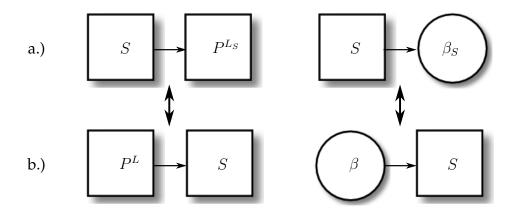

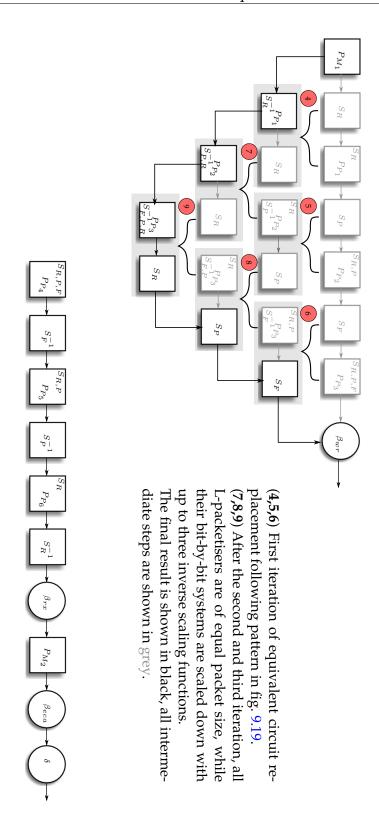

| 9.19         | Equivalent Circuits for Scalers                                                                                                                                                                                                                     | 174        |

| 9.20         | Introduction of Symbols for static Delays and WR Network                                                                                                                                                                                            | 175        |

| 9.21         | Replacement of DM Scalers                                                                                                                                                                                                                           | 176        |

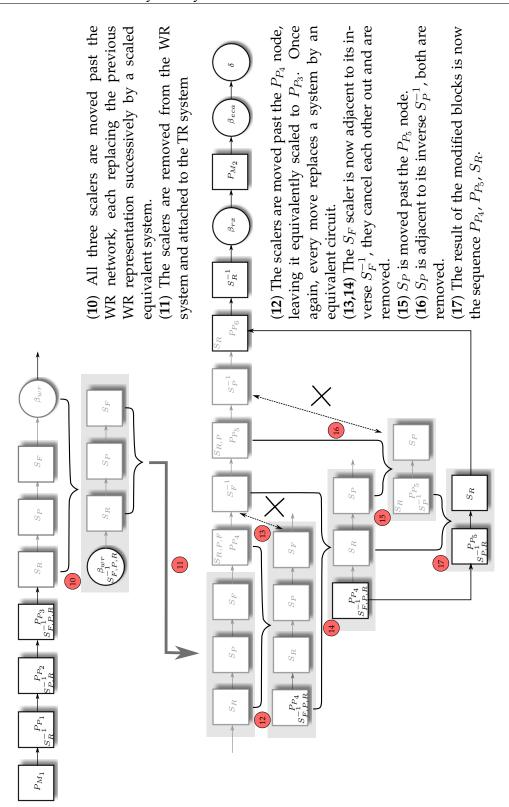

| 9.22         | Scaling WR NW and Replacement of TR Scalers                                                                                                                                                                                                         | 177        |

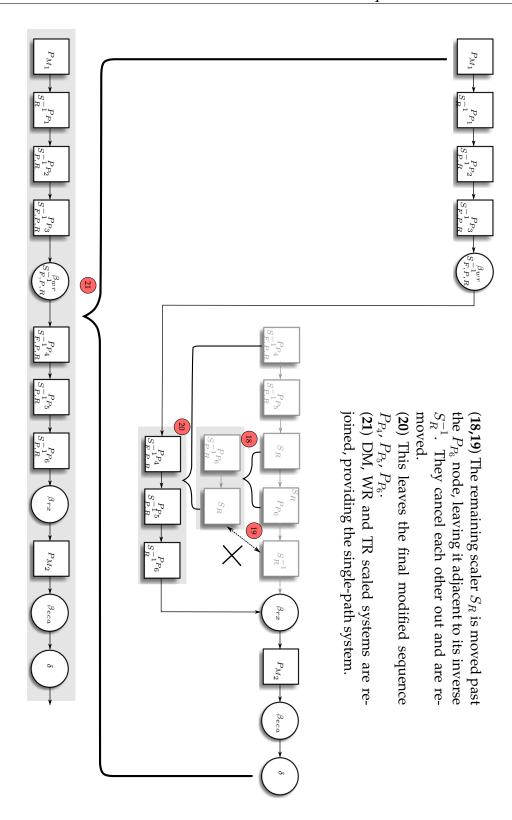

| 9.23         | Final TR Scaler Replacement and Join with DM Blocks                                                                                                                                                                                                 | 178        |

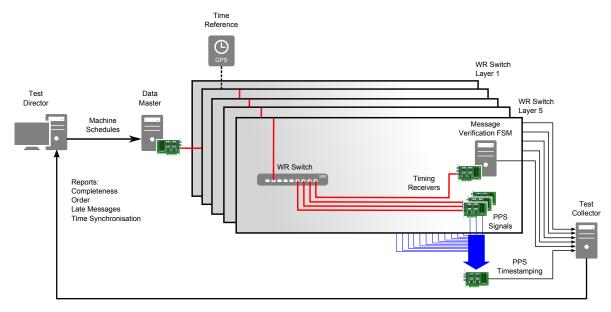

| 10.1         | GSI Timing Test Facility, Schematic of Verification System                                                                                                                                                                                          | 186        |

| 10.2         | Screenshot of Delay Analysis with DiscoDNC                                                                                                                                                                                                          | 188        |

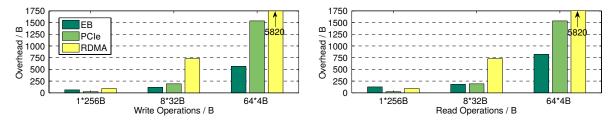

| 10.3         | Overhead of EB, PCIe, and RDMA when transmitting 256 Bytes read and write operations, 32 Bit word width. EtherBone distinctly                                                                                                                       | 190        |

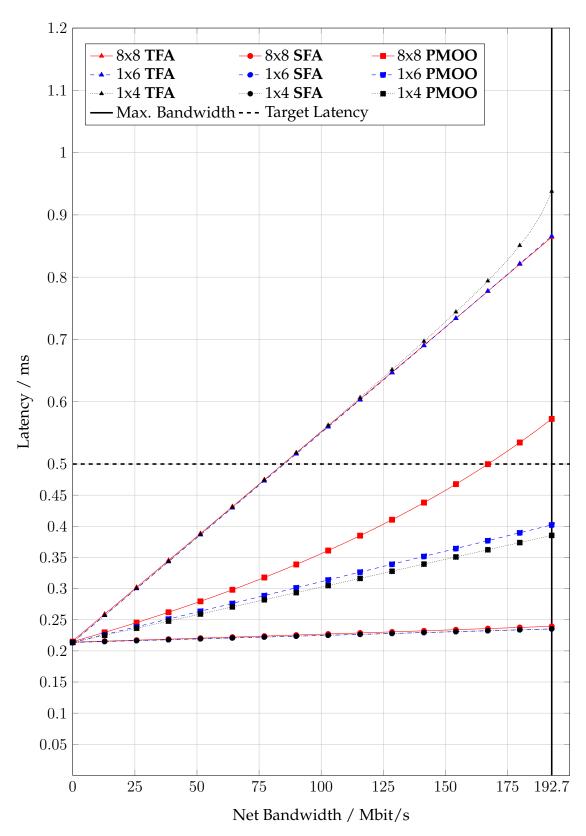

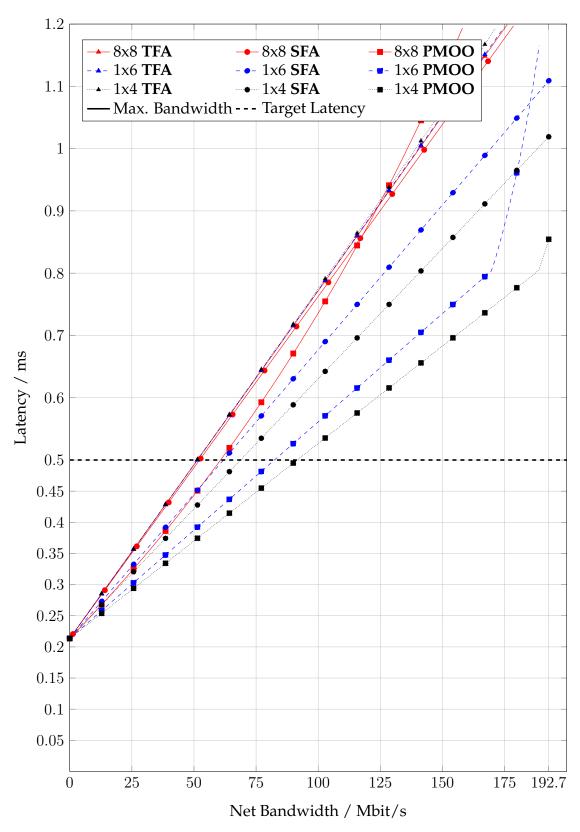

| 10.5         | excels in random access operations and block writes [93] FAIR CS Simulation, command latency bound over bandwidth. CPU x Threads equals the number of flows per type of analysis (marker                                                            | 190        |

|              | shape). Infinum of curves of equal colours shows the corresponding                                                                                                                                                                                  |            |

| 10.6         | latency bound                                                                                                                                                                                                                                       | 194        |

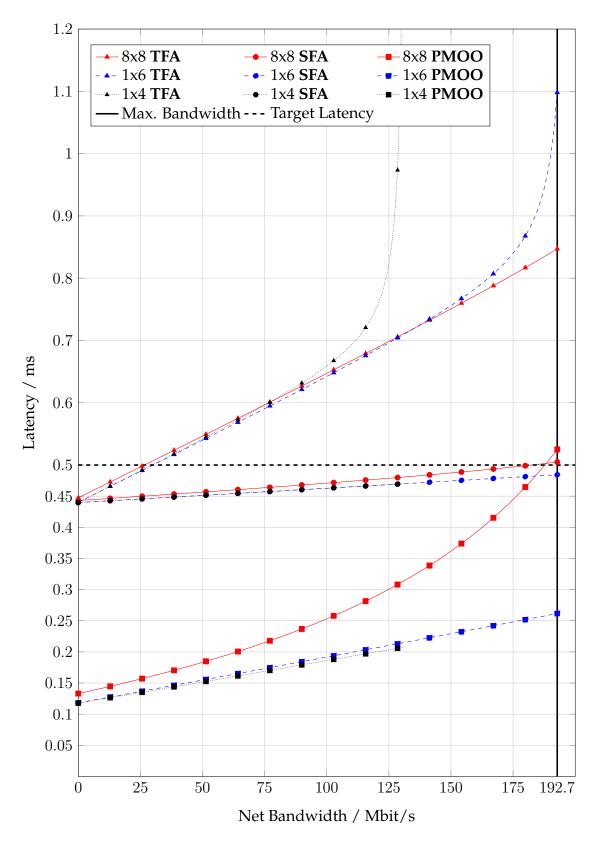

| 10.6         | FAIR CS Tunnel Influence Simulation, command latency bound over bandwidth. Removal of the tunneling effect on messages leads to a strong latency in groups are the 10 F.                                                                            | 107        |

| 10.7         | strong latency increase compared to 10.5                                                                                                                                                                                                            | 196        |

|              | (8 x 8) PMOO and SFA analyses (red squares and circles) show the goal of a 500 µs latency bound can be guaranteed up to 187 Mbit/s.                                                                                                                 |            |

|              | This more than satisfies the goal of 100 Mbit/s net bandwidth (see 4.6)                                                                                                                                                                             |            |

|              |                                                                                                                                                                                                                                                     | 197        |

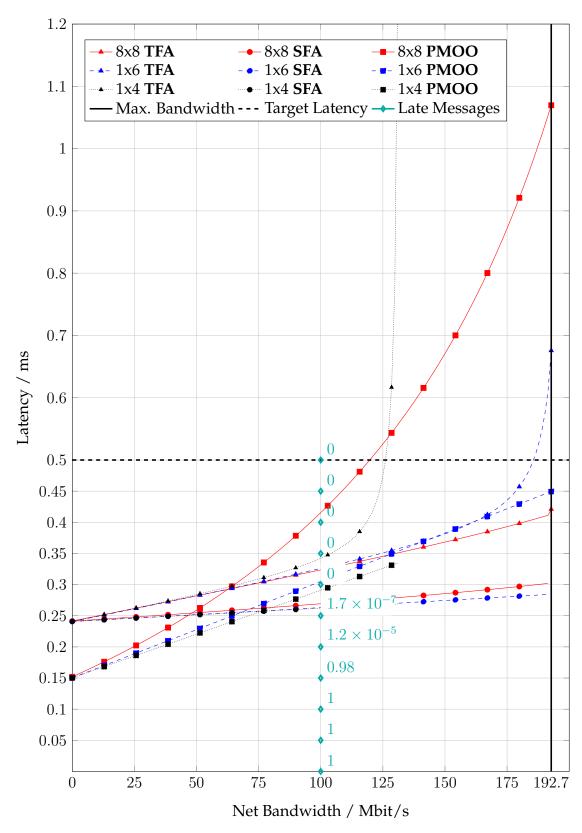

| 10.8         | MTS Simulation, command latency over bandwidth. Real MTS's ratio of late messages to messages at 100 Mbit/s (table 10.3) is shown                                                                                                                   | 1),        |

|              | in cyan. Position on the y-axis corresponds to latency budget, the number to the observed ratio. Ratios of 0 show that budgets above                                                                                                                | 400        |

| 10.9         | the curves' infinum ensured timely delivery                                                                                                                                                                                                         | 199<br>202 |

| 10.7         |                                                                                                                                                                                                                                                     |            |

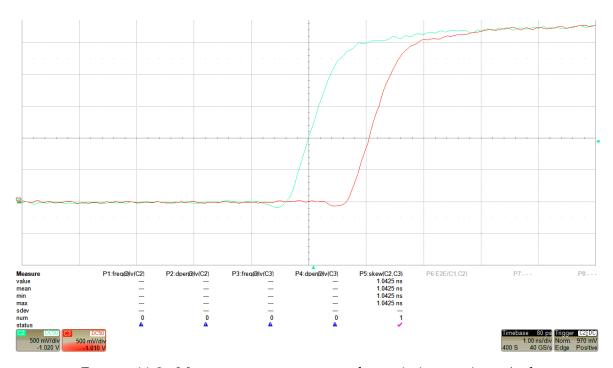

| 11.1<br>11.2 | 3D Model of the CRYRING Synchrotron and Injector [144] Measurement on outputs of two timing receivers (red and green curves). Time difference between curves (P5 skew measurement) shows the achieved timing resolution and accuracy when executing | 208        |

|              | DM commands for two pulses offset by 1 ns                                                                                                                                                                                                           | 211        |

| 11.3         | Excerpt from the Control System Interface Design Process                                                                                                                                                                                            | 214        |

## **List of Tables**

| <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Performance of Atomic Clocks                                                                             | 15<br>25<br>31                                                        |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 3.1                                           | Particle Accelerator Devices and Timing Requirements                                                     | 45                                                                    |

| 4.1                                           | Delay estimation for control messages Case for 5 Switches, 2 km link length, Message Size 500 and 1500 B | 60                                                                    |

| 5.1                                           | RTOS latency measurement results [84] Times in $\mu$ s                                                   | 66                                                                    |

| 5.2                                           | Simple Example of a Logic table In DNF: not( <b>A</b> ) and <b>B</b> or <b>A</b> and not( <b>B</b> )     | 67                                                                    |

| 8.1<br>8.2                                    | Execution Time per LM32-Instruction                                                                      | 134<br>134                                                            |

| 10.1<br>10.2<br>10.3                          | Data Master Features                                                                                     | 200<br>201                                                            |

|                                               | Net Bandwidth in the Minimal Test System                                                                 | 203                                                                   |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6        | Publications with Contributions from this Research Work Rate Scaling Factors for all Models              | <ul><li>221</li><li>221</li><li>222</li><li>223</li><li>224</li></ul> |

| <b></b> .                                     | for WR Systems without QoS (TTF, Mini Test)                                                              | 225                                                                   |

#### List of Abbreviations

**ACM** Association for Computing Machinery

ADC Analogue-to-Digital Converter

**ADEV** Allan Deviation

AES Advanced Encryption Standard ARP Address Resolution Protocol

ASIC Application Specific Integrated Circuit

B2B Bunch to Bucket transferBPC Beam Production Chain

BP Beam Process

CB CrossBar

**CERN** European Centre for Nuclear Research

CMD-Q Command Queue

**CNF** Conjunctive Normal Form

CORBA Common Object Request Broker Architecture

CPLD Complex Programmable Logic Device

CPU Central Processing Unit

CRC Cyclic Redundancy Check

CS Control System

DAC Digital-to-Analogue Converter

DC Direct Current

DDS Direct Digital Synthesis

**DESY** Deutsches Elektronen Synchrotron (German Electron Synchrotron)

**DHCP** Dynamic Host Configuration Protocol

DM Data Master

DNF Disjunctive Normal FormDSP Digital Signal Processor

**EB** Etherbone

EBS Etherbone Master EBS Etherbone Slave

ECA Event Condition Action unit

**EDF** Earliest Deadline First

**EPICS** Experimental Physics and Industrial Control System

Eth IEEE 802.3 Ethernet

FAIR Facility for Antiproton and Ion Research

FEC Forward Error CorrectionFH University of Applied Sciences

FIFO First In, First Out FOI Flow Of Interest

**FPGA** Field Programmable Gate Array

FSM Finite State Machine

GbE Gigabit Ethernet

GMT Greenwich Mean Time

GPS Global Positioning System

**GSI** GSI-Helmholtz Centre for Heavy Ion Research

HDL Hardware Description Language

**HP** High Priority

**IEEE** Institute of Electrical and Electronics Engineers

**IETF** Internet Engineering Task Force

IO Input/Output

**IP** Internet Protocol Version 4

IRIG Inter Range Instrumentation GroupITU International Telecommunication Union

JTAG Joint Test Action Group LHC Large Hadron Collider LINAC Linear Accelerator

LM32 Lattice Mico 32 Processor

lo left over service LP Low Priority

LVDS Low Voltage Differential Signalling

MCU Microcontroller Unit

MSI Message Signalled Interrupt

MTS Minimal Test System

MUX Multiplexer

NCO Numerically Controlled Oscillator

NC Network Calculus

NIC Network Integrated Controller NTP Network Timing Protocol

OSI Open Systems Interconnection Model

PAL Programmable Array Logic

**PBOO** Pay Burst Only Once

PCIe Peripheral Component Interconnect express

PGS Packetised Greedy Shapers

PHY Physical interface

PLA Programmable Logic Array

PLC Programmable Logic Controller

PLL Phase Locked Loop

PMOO Pay Multiplexing Only Once (Analysis)

PPS Pulse Per Second PQ Priority Queue

**PSCED** Packetised Scheduler, Earliest Deadline First

PTP Precision Time Protocol

OoS Quality of Service

Quality of Service

**RDMA** Remote Direct Memory Access

RF Radio Frequency

RR Round Robin

RTC Realtime Clock

RTOS Realtime Operating System

RTS Realtime System

**RX** Receiver

**SCPU** Soft Central Processing Unit

SDB Self Describing Bus

SDH Synchronous Digital Hierarchy

SERDES SERialiser / DESerialiser

SFA Separate Flow Analysis

SI International System of Units

**SNMP** Simple Network Management Protocol

**SOAP** Simple Object Access Protocol

SoC System on a Chip

**SONET** Synchronous Optical Networking

SSL Secure Socket LayerST Standard Time

SyncE

TAI

International Atomic Time

TCP

Transmission Control Protocol

TDC

Time to Digital Converter

TFA Total Flow Analysis

TLU Timestamp Latch Unit

TS Timestamp

TTF Timing Test Facility

TX Transceiver

UDP User Datagram ProtocolUSB Universal Serial Bus

UTC Coordinated Universal Time

UT Universal Time

VAT Virtual Address Table

VC(X)O Voltage Controlled (Crystal) Oscillator

VME Versa Module Eurocard-bus

WB Wishbone

WBM Wishbone Slave

WBS Wishbone Master

WR White Rabbit

# **List of Symbols**

$egin{array}{ll} R & {

m resistance} & \Omega \, ({

m V/A}) \\ C & {

m capacitance} & {

m F} \, ({

m V/C}) \\ L & {

m inductance} & {

m H} \, ({

m V} \, {

m s/A}) \\ \end{array}$

$\omega \quad \text{angular frequency} \quad \text{rad} \quad$

To Markus

# Part I Context and Background

## Chapter 1

#### Introduction

This chapter aims to give a general overview of this thesis. The context and motivation for this work are explained, followed by a detailed breakdown of research methodology. Moreover, the contribution to knowledge and its impact are presented. The structure of the thesis is then outlined, complemented by short summaries of all chapters.

#### 1.1 Motivation

The motivation for this thesis sprang from the need of a new type of control system (CS) for large physics experiments, which can utilise high accuracy timing. It was researched and developed in the context of a case study for the control of particle accelerator facilities.

"White Rabbit" (WR), the underlying time synchronisation technology, was an initiative started in 2008 by the European Centre for Nuclear Research (CERN) and initially aimed at the modernisation of the CS of the Large Hadron Collider (LHC) at CERN in Geneva, Switzerland. At the time, the GSI-Helmholtz Centre for Heavy Ion Research (GSI), in Darmstadt, Germany, took an interest in evaluating suitable technologies for a CS modernisation and a new CS for the upcoming Facility for Antiproton and Ion Research (FAIR), which will become a major extension to the GSI accelerator facilities.

Research and development of WR successively became a close collaboration between CERN and GSI/FAIR. The case study in this thesis is based on a CS design suitable for the FAIR accelerators and GSI facilities. The joint FAIR research complex is planned to go into operation in 2018.

#### 1.2 Research Methodology

This thesis is dedicated to the problem of achieving deterministic control of large realtime systems under the assumption of a common, highly accurate notion of absolute time. The use of WR as the underlying time distribution system is axiomatic, as it is based on a management decision prior to the start of this work. An evaluation in greater depth within the scope of this thesis (see subsection 2.7.1) could confirm that the properties of WR are sufficient for such a concept. The working hypothesis is that a such a CS can be conceived as a deterministic, alarm based system, capable

of utilising the full accuracy of the WR time distribution scheme to synchronously generate or distribute signals and assign timestamps to inputs.

Choice of Methodology A hypothesis can either be tested by experiment or by theoretical proof, i.e. trying to, by logical deduction, either confirm all of its aspects or refute one of them. For the research in this thesis, an experimental approach was chosen. The reason for this decision was that the proposed hypothetical system is complex, it consists of a combination of a large number of physical and logical problems to overcome. To obtain a rigorous result in a meaningful timeframe, the analysis must be built onto known theoretical models. This means the problems of the hypothetical system must be separable and transferable to known problems for which solutions have been found in order to prove or refute partial aspects. The advantage of a theoretical approach is that if the system can be modelled, the complete behaviour will be calculable. On the downside, since neither the separability nor the existence of known analogue problems is guaranteed, it is very possible to reach an impasse in research within the given time frame.

An experimental approach, on the other hand, allows black-box tests of complex systems to be conducted quickly, provided they can be built. Separation of the experiment into partial systems is also possible, provided all inputs and outputs can be observed. Since GSI could provide prototype implementations of the underlying WR time distribution infrastructure from the very beginning, it was likely that an adequate experiment setup to either prove or refute the hypothesis could be built. This original prototype hardware and all that were devised within the scope of this thesis feature industry standard interfaces, meaning all of the system's inputs and outputs could be accurately monitored using proven and well documented technology, such as high end oscilloscopes and network analysers.

**Objectives** The purpose of the primary research is the provision of a concept for a highly accurate CS, scalable to thousands of machines and distances of several kilometres. In conjunction with the case study (see subsection 4.6), three main objectives were defined:

- Scale in number of devices

- Scale in distance

- Accuracy of timing

The first objective requires evidence and/or theoretical justification that the system will be able to support the required number of devices and in consequence provide the required bandwidth, while the second objective requires evidence that the system is able to cover the required geographic distance. The third objective is the most complex, as it requires for the requested synchronicity, peak response time (latency) and time resolution.

**Research Objects** The primary research covers three distinct objects. The first is the master CS unit, which was named "Data Master" (DM) (chapter 7, 8). It has to

generate and deliver control messages to all endpoints in order to control machines. The second object is a concept for deterministic communication between WR platforms, which has been named "Etherbone" network protocol (EB) (chapter 6).

The definition of the third research object emanated from the necessity to verify the others. In order to show that deterministic control can be guaranteed in general and not only for a specific test case, bounds for its application were required. The third object therefore became the conception of a simulation model to provide bounds within which the CS's operation is guaranteed to be deterministic (chapter 9). The model must be usable at run time, although it does not need to satisfy hard realtime constraints.

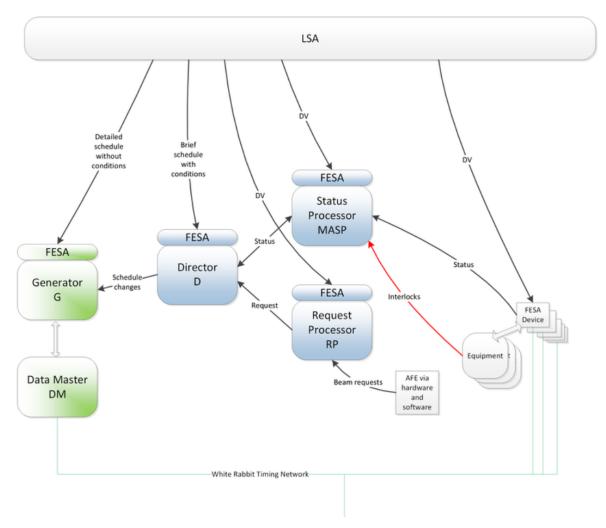

FIGURE 1.1: Overview of realtime CS and Settings Management. Endpoints (EP) receive both commands and set values. Scope of Primary Research is shown in grey.

Scope The term "control system" will be used throughout this thesis in the context of deterministic, hard realtime control. The hypothesis assumes an approach as an alarm based system, which separates commands and set values. Figure 1.1 shows the distinction. The CS instructs machines what to do when during runtime (green timeline). The corresponding set values, i.e. how the machine has to act, are distributed beforehand in a relaxed timeframe by the settings management system. The scope of primary research is indicated by the grey shaded area and the relation of the research objectives, DM, EB and simulation model, to settings management and endpoints (EP) is shown. Set values are data sets that describe the desired behaviour of specific EPs. In the context of a particle accelerator, this could, for example be the output current of a power supply (blue curve) or a voltage applied to an electrode (red curve).

#### 1.2.1 Research

**Literature Review** The origin of the literature review was centred around publications associated with WR. Most of the related work used in this thesis was obtained from online libraries, such as the IEEE Xplore digital library [1], the ACM digital library [2] and Springer Online [3]. Searches for papers, conference proceedings and journal articles were conducted by search engines such as Google Scholar [4] and CiteSeerX [5]. Most of the employed textbooks were obtained from GSI's on site library or interlibrary loans, the remaining books were perused online by means of the Google Books service [6].

The majority of unpublished sources was GSI/FAIR internal material, such as presentations, technical notes and specification documents for FAIR, which provided information on future machine requirements, compatibility to legacy equipment and management decisions. Yet more background information was acquired from private communications with accelerator physicists and operating engineers at GSI/FAIR. The remaining unpublished sources were comprised of documents in the Open Hardware Repository (OHWR), a website created by CERN to coordinate development and host source code and documentation for WR related projects and other programming or hardware related websites.

**Detailed specifications** Constraints and use-cases for the approach were obtained from secondary research into existing CSs, available field bus technology, planned experiments at FAIR and the architecture and properties of WR (chapter 4). The related sources stemmed from publications on WR and CSs of particle accelerators, from unpublished FAIR documents and private communication.

**Technology** The requirements gathered for the detailed specifications were used as the foundation for a survey of suitable technologies for development of a prototype system. The results did not indicate conflicts with the technology present in the underlying WR system. The corresponding research mainly relied on tertiary sources, such as data sheets, application notes and manuals (chapter 5) and secondary accounts from hardware engineers at GSI about their experiences with current technology in hard realtime scenarios.

Existing systems at other sites

Existing CSs at accelerators such as GSI, CERN, Diamond and DESY were evaluated in the course of the case study (see chapter 4.2.2). The secondary research into this area indicated that nearly all sites feature standard PCs and servers, which are not realtime capable. They also all use VME and industrial PCs running realtime Kernels, as well as programmable logic controllers (PLC). Both are able to achieve determinism down to microseconds. Finally, all the sites also have an optical clock distribution system, accurate to low picosecond or even femtosecond range. The only exception was CERN, which also provided UTC time accurate to nanoseconds. None of the investigated cases provided a generic control approach accurate to sub-nanosecond level. This very niche is the intended target of the new CS approach.

**Future Plans at FAIR** In 2018, not all accelerators of the FAIR complex will be completed and in operation. The new CS approach based on the research in this thesis and other research work at GSI is planned to be used for a retro-fitting of GSI's synchrotron. This means a replacement of the old GSI technology and running its main synchrotron, SIS18 with the new CS. This proposition is building on experience already gathered from controlling the smaller CRYRING accelerator. The CS approach will be expanded, tested and adjusted as necessary to control the whole FAIR facility in 2025.

### 1.2.2 Development

**Prototype Design** Based on the defined objectives, plans were specified to enable development of prototype systems of the DM and the EB protocol. Development occurred in both cases over several iterations, each intermitted by a phase of tests, presentation to the WR developer community and, if necessary, adjustment of the approach according to feedback and results.

Test Design and Equipment To test the hypothesis, hardware proving grounds for the prototypes were created. Variables were isolated as far as feasible by employing multiple different testbeds at different levels of integration. The lowest level were individual tests of sub-components, whose performance in terms of reliability, determinism, latency, and bandwidth was directly measured. The first step were unit tests by simulation, using randomised test data. These were followed up by integration tests on prototype hardware, verifying the latency, determinism and bandwidth predicted by the simulation. This was achieved by the application of on-chip logic analysers, profiling code, network analysers and oscilloscopes. The same set of tools was used to measure all quantitative targets imposed by the case study, allowing an accuracy between 8 ns for logic analysers and profiling code, 1 ns for timestamping by verified prototypes and below 20 ps for the oscilloscopes.

To conduct tests on higher abstraction levels, complete CS setups were assembled, consisting of a DM, WR network switches and up to several dozen CS endpoints. These scenarios were devised to run both short and long term reliability tests with randomised test data. To ensure the influence of individual platforms did not dominate the results, different constellations were created.

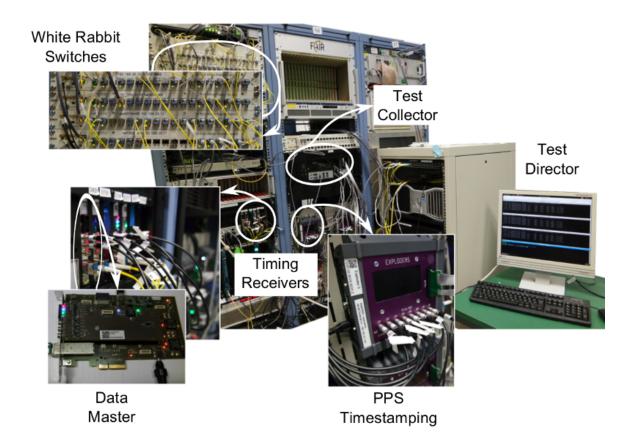

**Test** The tests cover, among others, scenarios such as 1 on 1 connections, test of time distribution only, high traffic scenarios and regular CS operation. To ensure consistency, these testbeds are persistent. An example can be found in chapter 10, "Timing Test Facility", figure 10.1 and figure 10.9. Ongoing development was verified on a daily basis by a continuous integration system, running standardised tests to ensure new developments did not negatively influence system performance.

**Replicability** All source code used in the FAIR CS design is open source and can be freely downloaded to replicate test cases described in this thesis. So are most hardware designs for WR infrastructure, easily allowing the replication of these experiments by others. Unfortunately, legal issues prevented public release of the DM

hardware specifications and several other GSI form factors to this day. It is yet unknown if and when a public release will occur. However, it is possible for interested parties to develop a suitable platform for the DM based on the freely available open hardware form factor designs [7].

**Analysis and Conclusion** Because the high level testbeds were run for long times without interruption (several weeks) and for more than a year in total, sending and receiving billions of control messages, a high degree of confidence in system performance could be established. This was further enhanced by the successful control of a production system in the form of a real accelerator since mid 2015 by a FAIR CS prototype, including the DM and EB (see chapter 10).

# 1.3 Contribution to Knowledge

There are a large number of existing CS designs available today, some of them established and well proven. The work in this thesis aims to improve timing accuracy and resolution in CSs by several orders of magnitude, while simultaneously introducing a new level of determinism, flexibility and scalability. This sets it apart from all other architectures published today.

In this thesis, it is shown, theoretically, and by experimental validation, that an alarm-based CS with a timing resolution of 1 ns is feasible. It is further theoretically shown that the proposed approach does scale to several thousand controlled machines and is validated for more than a hundred endpoints. In addition, it is shown that the proposed CS supports fully deterministic, parallel control processes, synchronised at the full accuracy of the system. Moreover, a control scheme that allows machine schedules to be steered at runtime is presented and has been validated. It is also shown that control loop speed is only limited by external input and control message rate is only limited by network bandwidth. It is further shown theoretically that timely arrival can be guaranteed for trees of alternative command sequences, known ahead of time, as well as for limited changes during runtime.

# 1.4 Generalisation and Impact

The results of this work are already in use at GSI/FAIR [8], CERN and other institutions. Apart from the field of particle accelerators, wired machine coordination over several kilometres at nanosecond accuracy can provide the greatest benefit to the telecommunication industry, where phase antennas benefit from high accuracy synchronisation. More details and examples of projects already employing WR and EB based timing and CSs can be found in chapter 11.3.3 on page 208. There are more than 20 institutions employing WR (usually with EB) and a complete list can be found at the OHWR Website [9].

#### 1.4.1 Thesis Structure

FIGURE 1.2: Thesis Structure Coloured Slices indicate Parts, Arrows mark Dependencies between Chapters

As shown in figure 1.2, the thesis is grouped into four main parts, indicated by the coloured slices. The dependencies between individual chapters are marked with solid lines, starting at the chapter that is the prerequisite and ending with an arrowhead at the chapter depending on the content. Content which is not strictly necessary, but considered helpful to understanding, is connected with dashed lines. The four parts are:

**I – Context and Background** Apart from this general introduction, the first technical part is an introduction to the fields of timekeeping and particle accelerator

physics (chapter 2 and 3). Both are required to understand the problems discussed in the case study. The former provides the necessary background for high precision timing systems, while the latter covers the basic theory of particle accelerators and their CS requirements. They form the introductory material for understanding the problems discussed in the case study.

**II – Problem Analysis** The FAIR accelerator case study is presented and the problems formulated (chapter 4). This case study analyses existing accelerator CSs, given requirements and planned experiments for FAIR and deduces the imposed requirements for a suitable CS. Building on this case study, a technology survey (chapter 5) follows, which contains a detailed discussion of suitable hardware and software platforms.

**III – Approach and Implementation** The third part contains different approaches, their discussion, topic specific literature review and solutions to partial problems. Chapter 6 covers deterministic data exchange and the development of the EB protocol. Chapter 7 and 8 contain the discussion on hardware and firmware of the main control unit, the DM. Finally, chapter 9 provides a theoretical model for the calculation of the CS's maximum end-to-end latency. This delivers the boundaries within which deterministic operation of the CS can be guaranteed.

**IV – Conclusion** Finally, all chapters from part III are evaluated in terms of their fitness as a solution to the problems presented in part II. This single chapter presents the methods used for verification as well as the results from experiments and simulation. It then draws a conclusion and indicates future work (chapter 10).

#### 1.4.2 List of Publications

A complete list of publications containing contributions from my research that was undertaken for this thesis or already existing material that has influenced this thesis can be found in appendix C on page 219.

# **Chapter 2**

# **Timekeeping**

### 2.1 Overview

A standardised, common system of timekeeping is one of the most crucial agreements necessary for life in a modern civilisation. Over the years, several standards have been created to address this necessity. By now most of the requirements have been successfully met by ever more accurate, stable or more generic systems. There are at least 5 different timekeeping systems in use today (as of 2016), their design criteria spanning from solar-cycle oriented human life, simplicity and stability, astronomic scenarios and even relativistic time. The first part of this section will cover the basics of clocks and their possible accuracy, time systems and their application and finally their digital representations. The second part aims to give a basic understanding of oscillators and their synchronisation and will further introduce time distribution systems.

## 2.1.1 Terminology

When talking about time, clocks, oscillators and the synchronisation of systems, there are specialised terms which will be introduced here. Some of these terms also have widely used colloquial meanings and require clarification.

Accuracy and Precision While "accuracy" is colloquially synonymous with "precision", scientifically there is a strong distinction between the two. The common scientific definition is "accuracy" being the systematic and "precision" the random contribution to error, with error being the difference between the measured value and the expected value. The expected value is either a theoretical or a reference value. An extended terminology for accuracy and precision is given in the ISO 5725 standard [10]. According to the standard, "trueness" describes the systematic error, often expressed as a bias. "Precision" describes only the random error, this is usually expressed as standard deviation. "Accuracy" is defined as the resulting overall quality, the closeness between the observed value and the true or reference value. In the context of this thesis, the definition will adhere to the ISO 5725 standard.

**Clock** The term "clock" has two meanings in the present context. The common definition of a clock "A mechanical or electrical device for measuring time ...", whereas in computing, a clock is "An electronic device used to initiate and synchronise internal

operations" [11]. In order to clarify this, the former will be called a "clock", the latter will be called an "oscillator" when referring to the physical device and a "clock signal" or "sample clock" in the context of device synchronisation in a computer.

**Skew** Skew is usually defined as the offset between the edge of a clock signal and its corresponding data. This deviation varies for different points in the same synchronous digital system due to propagation delay.

**Jitter** When talking about oscillators and especially clock signals, the terms "jitter" and "skew" are often used. There are actually multiple definitions of jitter which are commonly used [12]. The most important ones are:

- Period Jitter, the deviation of cycle length to the ideal period

- Cycle to Cycle Jitter, the deviation of cycle length to the adjacent cycle's length

- Long Term Jitter, the deviation of a clock signal from its ideal position over several cycles

- Phase Jitter, the integration of phase noise over a given spectral interval

- Time Interval Error, the deviation of the actual position of edge from the ideal position of said edge

In the context of timekeeping, cycle-to-cycle jitter is the most important property for short term stability. The Time Interval Error can be an important parameter for synchronous digital systems, as it determines the maximum amount of skew before data is sampled at the wrong clock cycle.

**Synchronisation** This term is ambiguous and can either refer to the more general process of achieving a common notion of time or the phase and frequency alignment of two metronome-like oscillators. In this context, the general process will be called "time synchronisation" and oscillator synchronisation will be called "clock synchronisation" or "syntonisation".

#### 2.1.2 What it takes to measure time

A clock, or chronometer, is a measurement device, counting the occurrence of an event with a known length of time. A more general definition would be a chronometer consisting of:

- (a) A time "reckoner", which is a repeatable phenomenon whose motion or change of state is observable and obeys a definite law

- (b) A time reference, with respect to which the position or state of the time reckoner can be determined

These elements correspond to the two properties of time measurement: interval and epoch [13]. Or put briefly, a clock consists of an oscillator and a counter.

The accuracy of a clock is a complex interplay of a variety of factors. The resolution is determined by the frequency of the oscillator, because any measured time period cannot be smaller than the time between two events. When talking about clocks, there is a distinction between accuracy and stability [14]. The accuracy of a clock describes the closeness to a known time reference while stability only describes how reproducible its output is. Stability is usually described as a deviation from the mean, accuracy as closeness to the reference. The most common variant for expressing stability is the Allan deviation (ADEV).

# 2.2 Timekeeping History

The following is a short excursion on the history of timekeeping from the year 1700 onward. It covers the origin, the application, conversion between systems and the impact of legacies on modern timekeeping.

### 2.2.1 Navigation - the Driving Force for Clocks

A strong demand for accurate timekeeping came up in marine navigation. When navigating by celestial bodies like stars or planets, the observed angle between the horizon and such a body depends on time and the position on earth. The latter is given in polar coordinates, two angles and a distance: latitude (angle on the polar plane), longitude (angle on the rotational plane) and height. Barring accidents or freakish weather, ships are normally found at sea level, so height can safely be ignored in a marine context.

Earth's rotational axis is tilted about 23.5 degrees in relation to its orbital plane. When measuring from the same position on earth, the observed culmination angle of a star changes over the course of a year. Latitude can then be determined from angular tables, the time of year and the observation angle. For finding longitude, the time of day is required. Since earth does a full rotation once per day, the time of day at which the culmination of a celestial body can be observed strongly depends on the longitudinal position. In reverse, longitude can be determined from angular tables and knowing the current time at the location the tabular values were taken.

**The Longitude Problem** Finding longitude was an impossible navigation problem for centuries, because a very accurate time reference is needed. The following conversions shall illustrate the scale of the time influence for latitude and longitude calculation. For the sake of brevity in the following explanation, a simplified approach is used, ignoring the fact that earth is an ellipsoid.

As rough calculation for latitude based on almanac data [15] can quickly show that even without the time of day, just knowing the date, the maximum latitude error is  $\approx 23\,\mathrm{km}$ . However, earth rotates  $360^\circ$  in a day, making longitude calculation far more sensitive to time than latitude. Dividing the number of arc minutes per day by the number of seconds per day (eq. 2.1), we get an error per second of 0.25

arc minutes or 463 m. As eq. 2.1 shows, this means a clock being off by 1 min already produces a longitude error greater than the maximum possible latitude time error. Hence, historically, longitudinal navigation errors were more prominent. The probably most famous example of such an error is the Scilly naval disaster of 1707, which had an even higher death toll than the sinking of the Titanic in 1912.