#### **Acknowledgements**

- GSI Timing Team: Enkhbold Ochirsuren, Marcus Zweig [1], Stefan Rauch, Mathias Kreider, Martin Skorsky, Dietrich Beck, Frederic Ameil [2], Anna Ranz, Alexander Hahn, Michael Reese

- GSI ACC-IT Team: Maxim Itterman, Peter Pfister, Christoph Handel, Rosemarie Vincelli ...

- CERN Team: Greg Daniluk, Maciej Lipinski ...

- External: Alessandro Rubini, Adam Wujek ...

- ..

- [1] Michael, Martin and Marcus left; job opportunity https://www.gsi.de/en/jobscareer/job\_offers

- [2] Frederic is our new team leader :-)

## **WRC** Related Activities at GSI

- Short Overview

- Timing Receiver Node Form Factors

- New Form Factors

- What About WRPC v5?

- WR Switch firmware

## **GSI** from the Control System Perspective

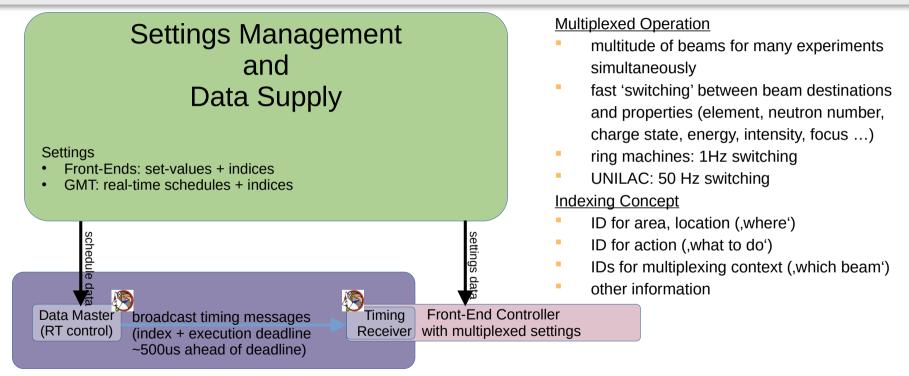

# Multiplexed Operation, Control System Stack and General Machine Timing

General Machine Timing System: trigger Front-Ends with multiplexing index on-time

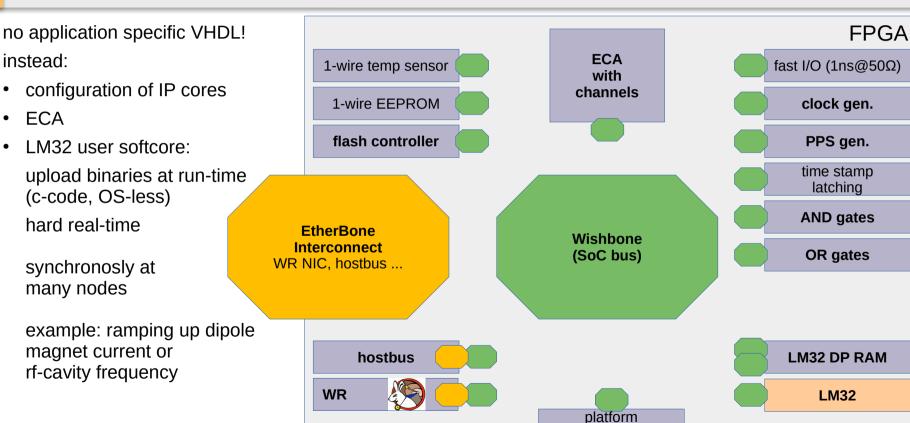

# Common Features for Timing Receiver Nodes 'Everything Happens in the FPGA'

December 2024

specific I/O/bus

**Common Features for Nodes ...**

**JTAG**

December 20

#### WR @ GSI, Status

- 67 69 (104 107) [333] WR switches for facility operation (in use) [on-site]

- mainly Creotech and Seven Solutions, some SyncTechnology

- v6.1 for all operational WRS

- SFP, mainly CBO with DDM

- 332 (416) [2296] WR nodes for facility operation (in use) [on-site]

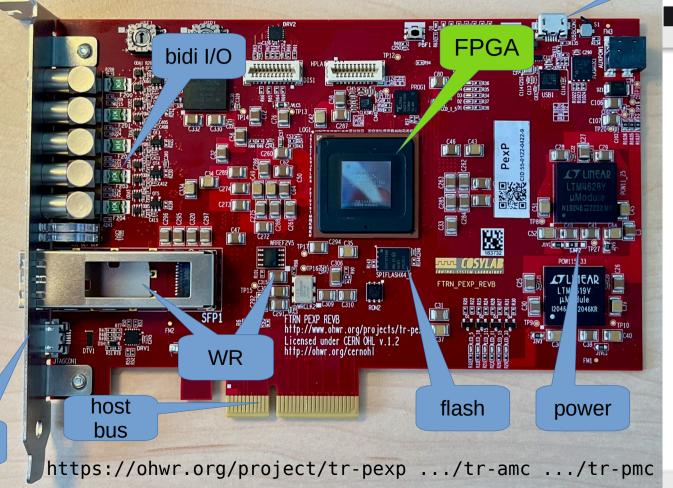

- OHWR: TR-PMC, TR-AMC, TR-PEXP; in-house: SCU (Scalable Control Unit, workhorse)

- Arria V GX, Arria II GX

- wrpc-v4.2

- https://github.com/GSI-CS-CO/bel\_projects, current release v6.3.1 ,fallout

- host systems

- SCU: COM Express

- non-SCU: uTCA, VME, IPC (1U), Server-PC, other

- PXE boot of ,ACO-Ramdisk' for Accelerator COntrol system

- other

## **New Timing Receiver (TR) Nodes I**

- Arria II about 1/3 of TR at GSI, mainly SCU3; old FPGA type

- Arria V about 2/3 of TR; formfactors 2x PCIe, AMC, PMC, standalone

- availability on the market is bad (feels like it becomes deprecated)

- maintaining gateware releases (FPGA images) requires a lot of effort

- many units and functionality inside our images

- use ,seed mining' to make the fitter happy somehow

- synthesis only possible with additional flip-flops and clock crossings

- not yet: dedicated platform for Data Master

- A 10 next generation Timing Receivers

- SCU5

- successor of SCU3, standard front-end controller for FAIR

- in-house development

- Pexarria10, two versions with different FPGA sizes

- small: node version with one SFP/White Rabbit interface, 2 user soft cores

- large: "Data Master" version with two SFPs/White Rabbit interfaces, 8+ user soft cores

- same FPGA footprint for both

- open source project on OHWR/GitHub/GitLab

#### **New Timing Receiver Nodes II**

- A10 TR to be contributed to WRC; relevant repos general-cores, wrpc-sw, wr-cores

- issues

- when the large FPGA is used, heating is a major issue

- dual White Rabbit kills PCIe, hard to fix, according to Intel/Altera problems inside the transceiver banks

- 1ns LVDS IOs do not work yet

- prime feature for TR nodes at GSI/FAIR (we don't use ,fine-delay' modules)

- 1ns granularity achieved by using differential 1GBit transceivers

- time stamping

- pulse generation

- porting from Quartus 18 to Quartus 23 requires a new hardware revision (clocking)

- only one 3V bank (not 3.3V!) -> level shifter madness

#### WRPC v5 @ GSI

- works on Arria2 and Arria10.

- ArriaV: WR unreliable frequent loss of lock

- Etherbone partially broken

- to be contributed to WRC; relevant repos general-cores, wrpc-sw, wr-cores

- requires a major gateware release

- for all (lots!) form factors used at GSI

- not only WR, but other GSI/FAIR specific things too

- lower priority than development of A10 Timing Receivers

- not for 2025, 2026 maybe ...

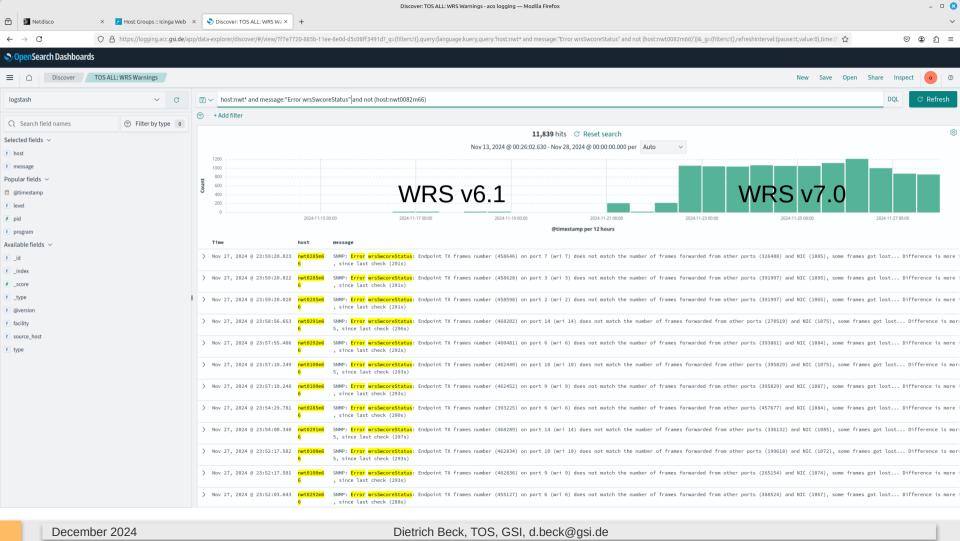

#### **WRS Firmware Upgrade**

- 21-22 Nov 2024: firmware update of all 107 White Rabbit switches from v6.1 to v7.0

- required changes in dot-config and new calibration parameters

- worked out very well

- only issue so far

- "Error wrsSwcoreStatus: Endpoint TX frames number (462775) on port 10 (wri 10) does not match the number of frames forwarded from other ports (134005) and NIC (1090), some frames got lost... Difference is **more than 5**, since last check (293s)"

- false positive

- issue shows up only in a dedicated network with frame rates 1.5 ... 2.5 kHz

- v6.1: less than 10 occurences per week

- v7.0: more than 100 occurences per hour

- proposal: configurable limit via dot-config (presently fixed limit of 5 frames)

- BTW: are there new calibration values for the fanless WRS from SynchTech?

#### **WRS Firmware Upgrade**

- 21-22 Nov 2024: firmware update of all 107 White Rabbit switches from v6.1 to v7.0

- required changes in dot-config and new calibration parameters

- worked out very well

- only issue so far

- "Error wrsSwcoreStatus: Endpoint TX frames number (462775) on port 10 (wri 10) does not match the number of frames forwarded from other ports (134005) and NIC (1090), some frames got lost... Difference is **more than 5**, since last check (293s)"

- false positive

- issue shows up only in a dedicated network with frame rates 1.5 ... 2.5 kHz

- v6.1: less than 10 occurences per week

- v7.0: more than 100 occurences per **hour**

- proposal: configurable limit via dot-config (presently fixed limit of 5 frames)

- BTW: are there new calibration values for the fanless WRS from SynchTech?

#### **Summary**

- GSI joined WRC in November 2024

- working on new hardware platforms based on Arria 10 FPGAs

- working on migration to WRPC v5 (low priority)

- updated all WRS to v7.0

# **Thank You For Your Attention**